## Integrated Circuit D Final Report

Submission Due: 2021/2/7(Mon)08:45 (via WebClass)

※結果だけでなく、<u>導出過程を含めて</u>記述すること。また講義資料以外で参考にしたものがある場合(Web ページや友人との相談も含む)は、必ず出典を明記すること。<u>出典を示さずに引用が確認された場合は不正行為とみなします</u>。また解答は日本語でも英語でもよい。

出典の表記形式(例)

- •秋田純一「はじめての電子回路 15 講」, p.10-12 (※書籍の場合。著者名、書名、ページ):

- •https://ifdl.jp/akita/class/ (※Web ページの場合。URL)

- ・○○君と相談 (※友人等との相談の場合)

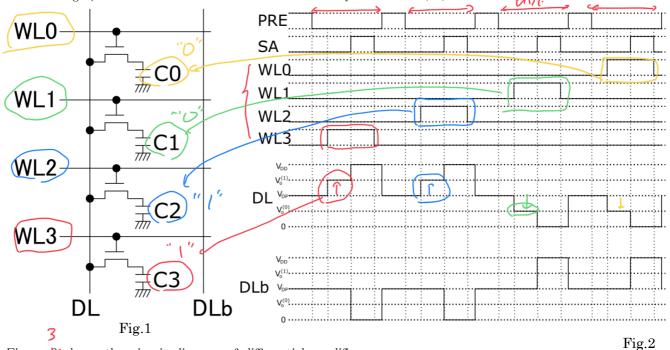

- 1. Figure 1 illustrates the operation waveform of DRAM cell array for 4 bits, whose circuit configuration is shown in Fig.2. Answer the status (charged or discharged) of each capacitor in initial condition for CO to C3; write '1' for charged, and '0' for discharged. Answer the reason briefly why you have chosen their status. Note that PRE and SA are the precharge and the sense amplifier control signal, respectively, and the circuits for pre-charge and sense amplifier are not shown in Fig.2, but assume that these circuits are correctly connected. (30)

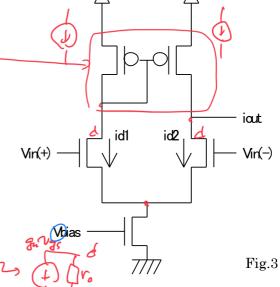

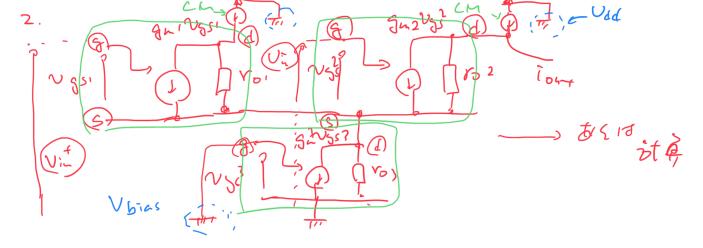

2. Figure \*\* shows the circuit diagram of differential amplifier.

Describe it small-signal equivalent circuit. Note that the current mirror can be replaced as the constant current source.

(20)

5. Describe your reflection (振り返り) and impressions on what you have learnt in this class, in terms of how they effect your daily and long term life, and the context you have learnt in other classes. (10)

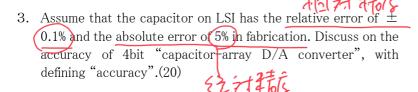

3. (a)  $C_0, C_1, C_2, C_3, C_6$   $C_0 = C + 0.05 C = (1 + 0.05) C = (0.98 C - 1.05) C$   $C_1 = C_0 + 0.001 C_0 = (1 + 0.001) C_0 = (0.99) C_0 - 1.001 C_0$   $C_3 = 2C_0 + 0.001 C_0$   $C_4 = 8 C_0 + C_1 = (0.98) C_1 = 0.98 C - 0.95 C_1$   $C_4 = 8 C_0 + C_1 = 0.98 C - 0.95 C_1$   $C_{10} = C_{10} + C_{10} +$