An Bn

PG

手書きノートのみ持込可です。解答はすべて解答用紙に、問題番号とともに導出過程も含めて記述すること。 80 点以上のみ単位認定の対象とします。

- 1. 桁上げ先見加算器(Carry Look-ahead Adder; CLA)は、入力  $A_n$ ,  $B_n$  から各桁の桁上がり  $C_n$  を先に求めることで高速化を図る加算器の構成方法である。なお以下では、最下位桁の桁上げ入力  $(C_{-1})$  は0 であるとする。 $(60 \, 6)$

- (1) 各桁の桁上げ信号  $C_0 \sim C_3$  を、マンチェスタキャリー連鎖(MCC)によって  $A_0 \sim A_3$  および  $B_0 \sim B_3$  から 求める回路の回路図を示せ。ただしプリチャージ信号を とし、入力  $A_n$ ,  $B_n$  から生成項  $G_n$  と伝播項  $P_n$  を生成する回路ブロック PG は図1の記号で示す機能ブロックとして用いてよい。(30点)

- (2) (2)の回路に、図2のような  $A_0 \cdot A_1 \cdot$  が与えたときの  $C_0 \sim C_3$  の電圧 の変化を、縦軸を電圧、横軸を時間とするグラフとして、 $A_0 \cdot A_1 \cdot$  とともに 同 一 座 標 軸 に 示 せ 。た だ し  $A_2 = A_3 = B_3 = 0$  (0V)、 $B_0 = B_1 = B_2 = 1$  (VDD)とし、図2中に点線で示した変化のタイミングを明示すること。(30点)

図 2

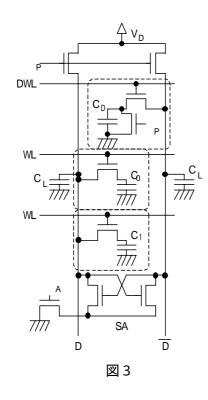

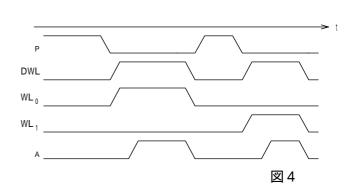

2. 図3のような DRAM の回路で、図4のような  $_P$ ・DWL・WL $_0$ ・WL $_1$ ・  $_A$  が与えられた場合のデータ線  $_P$ ・ $_D$  の電圧の変化を、縦軸を電圧、横軸を時間とするグラフとして、  $_P$ ・DWL・WL $_0$ ・WL $_1$ ・  $_A$  とともに同一座標軸に示せ。ただし図4中に点線で示した変化のタイミングや電圧変化量は明示すること。また  $_C$ = $_C$ 1、 $_C$ = $_C$ 0/2、 $_C$ 1=10 $_C$ 0 とし、MOS トランジスタの電流駆動能力は適宜仮定して構わない。なお初期状態で  $_C$ 1には電荷がなく、 $_C$ 1は電圧  $_C$ 1に充電されていたとする。(40点)