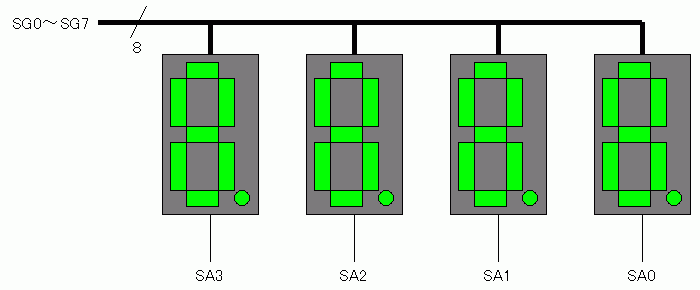

偙偺挷巕偱4寘傕偄偗偽傛偄傛偆偵巚偊傑偡偑丄巆擮側偑傜 偦偆娙扨偵偼偄偒傑偣傫丅 偲偄偆偺傕丄4屄偺7僙僌儊儞僩LED偼丄SG0乣SG7偑 嫟捠偵偮側偑偭偰偄傑偡丅 偮傑傝SG0='0'偲偡傞偲丄4寘偺偡傋偰偺7僙僌儊儞僩LED偺 忋偺LED(僙僌儊儞僩)偑揰摂偟偰偟傑偆偙偲偵側傝傑偡丅

偙偺挷巕偱4寘傕偄偗偽傛偄傛偆偵巚偊傑偡偑丄巆擮側偑傜

偦偆娙扨偵偼偄偒傑偣傫丅

偲偄偆偺傕丄4屄偺7僙僌儊儞僩LED偼丄SG0乣SG7偑

嫟捠偵偮側偑偭偰偄傑偡丅

偮傑傝SG0='0'偲偡傞偲丄4寘偺偡傋偰偺7僙僌儊儞僩LED偺

忋偺LED(僙僌儊儞僩)偑揰摂偟偰偟傑偆偙偲偵側傝傑偡丅

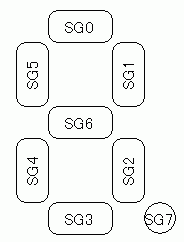

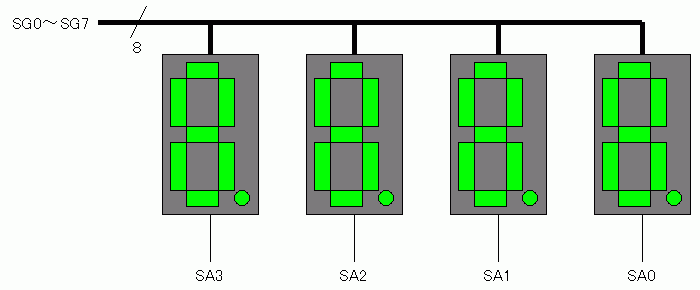

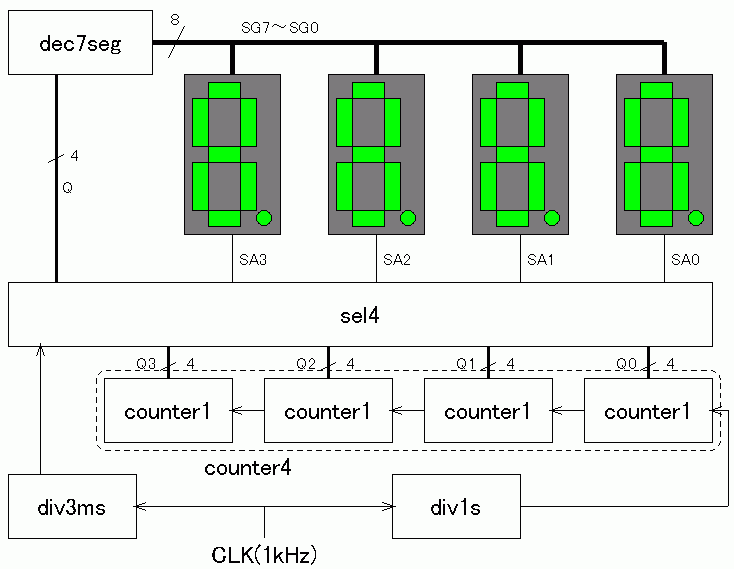

偙傟偱偼丄岲偒側4寘偺悢抣傪昞帵偱偒側偄傢偗偱偡偑丄 偦偺戙傢傝丄奺寘傪揰摂偝偣傞偐徚摂偝偣傞偐傪寛傔傞 SA0乣SA3偲偄偆怣崋偑偁傝丄偙傟傕FPGA偵偮側偑偭偰偄傑偡丅 偙傟偼丄(晧榑棟側偺偱)'0'偵側偭偨寘偺7僙僌儊儞僩LED偺傒丄 SG0乣SG7偵懳墳偟偰奺LED(僙僌儊儞僩)偑揰摂偡傞丄偲偄偆 婡擻傪傕偭偰偄傑偡丅

偙傟傪偆傑偔巊偆偲丄師偺4偮偺忬懺傪弴偵曄偊偰偄偗偽丄 1寘偢偮悢抣傪昞帵偱偒傞偙偲偵側傝傑偡丅

entity counter1 is

Port ( CLK : in STD_LOGIC;

RST : in STD_LOGIC;

Q : out STD_LOGIC_VECTOR (3 downto 0);

CO : out STD_LOGIC);

end counter1;

嶲峫丗愝寁椺

entity counter4 is

Port ( CLK : in STD_LOGIC;

RST : in STD_LOGIC;

Q0 : out STD_LOGIC_VECTOR (3 downto 0);

Q1 : out STD_LOGIC_VECTOR (3 downto 0);

Q2 : out STD_LOGIC_VECTOR (3 downto 0);

Q3 : out STD_LOGIC_VECTOR (3 downto 0);

CO : out STD_LOGIC);

end counter4;

嶲峫丗愝寁椺

entity dec7seg is

Port ( D : in STD_LOGIC_VECTOR (3 downto 0);

SG : out STD_LOGIC_VECTOR (7 downto 0));

end dec7seg;

entity sel4 is

Port ( CLK : in STD_LOGIC;

RST : in STD_LOGIC;

Q0 : in STD_LOGIC_VECTOR (3 downto 0);

Q1 : in STD_LOGIC_VECTOR (3 downto 0);

Q2 : in STD_LOGIC_VECTOR (3 downto 0);

Q3 : in STD_LOGIC_VECTOR (3 downto 0);

Q : out STD_LOGIC_VECTOR (3 downto 0);

SA : out STD_LOGIC_VECTOR (3 downto 0));

end sel4;

仸僸儞僩丗偙傟偼丄1偺寘乣1000偺寘傪昞帵偟偰偄傞忬懺4偮偺忬懺

SA0_ST乣SA3丵ST傪傕偮僗僥乕僩儅僔儞偲偟偰愝寁偱偒偦偆偱偡丅

entity div1s is

Port ( CLK : in STD_LOGIC;

CLK1S : out STD_LOGIC;

RST : in STD_LOGIC);

end div1s;

entity div3ms is

Port ( CLK : in STD_LOGIC;

CLK3MS : out STD_LOGIC;

RST : in STD_LOGIC);

end div3ms;

仸3ms偛偲偵寘偑愗傝懼傢傝丄4寘偱傂偲傑傢傝偱偡偐傜丄

昞帵偺揰柵偺廃婜偼3ms亊4=12ms丄偮傑傝栺80Hz偲偄偆偙偲偵側傝傑偡丅

entity top_counter4 is

Port ( CLK : in STD_LOGIC;

RST : in STD_LOGIC;

SG : out STD_LOGIC_VECTOR (7 downto 0);

SA : out STD_LOGIC_VECTOR (3 downto 0);

LED0 : out STD_LOGIC);

end top_counter4;

NET "CLK" LOC = "P18"; NET "RST" LOC = "P50"; NET "LED0" LOC = "P65"; NET "SG<7>" LOC = "P29"; NET "SG<6>" LOC = "P30"; NET "SG<5>" LOC = "P31"; NET "SG<4>" LOC = "P40"; NET "SG<3>" LOC = "P41"; NET "SG<2>" LOC = "P42"; NET "SG<1>" LOC = "P43"; NET "SG<0>" LOC = "P44"; NET "SA<3>" LOC = "P46"; NET "SA<2>" LOC = "P47"; NET "SA<1>" LOC = "P48"; NET "SA<0>" LOC = "P49";

NET "LED0" LOC = "P65"; NET "LED1" LOC = "P64"; NET "LED2" LOC = "P63"; NET "LED3" LOC = "P62"; NET "LED4" LOC = "P60"; NET "LED5" LOC = "P59"; NET "LED6" LOC = "P58"; NET "LED7" LOC = "P57"; NET "SWA" LOC = "P50"; NET "SWB" LOC = "P51"; NET "SWC" LOC = "P54"; NET "SWD" LOC = "P56"; NET "BUZ" LOC = "P96"; NET "CLK0" LOC = "P88"; NET "CLK1" LOC = "P91";