### 集積回路工学第2

集積回路工学研究室(MeRL) 秋田純一

### この講義の位置づけ

4年前期

3年後期

3年前期

2年後期

集積回路設計及び演習 [深山・秋田] 集積回路工学第2(情)・集積回路工学(電) [秋田] 集積回路工学第1(情)・デジタル回路(電) [北川] 半導体工学[森本] 半導体工学[北川] 情報システム工学科 電気電子システム工学科

## 各科目で取り扱う範囲

| 学期   | 科目          | 設計のレベル(表現の抽象度)                        |

|------|-------------|---------------------------------------|

| 4年前期 | 集積回路設計及び演習  | サブ-システムレベル(HDL記述、論理<br>合成、CPU設計)      |

| 3年後期 | 集積回路工学2     | サブ-システムレベル(要素回路)                      |

| 3年前期 | 集積回路工学1     | ゲートレベル・トランジスタレベル(レイアウト設計実習)           |

|      | 情報システム工学実験2 | トランジスタレベル(回路シミュレーション)                 |

| 2年後期 | 半導体工学       | 物理レベル:製造テクノロジとT-CAD<br>(プロセスシミュレーション) |

# 集積回路

### 集積回路ができるまで

- ロビデオ

- NHKスペシャル 「電子立国日本の自叙伝」(1991) (抜粋:18分程度)

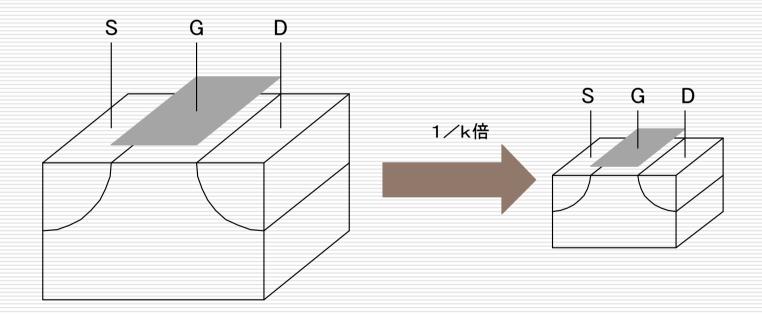

### スケーリング則

□ 集積回路を構成するMOSトランジスタを小さく すると・・・

### スケーリング則の効果

- □ 信号遅延=1/k(高速化)

- □ 消費電力=1/k²(低消費電力化)

- □ 集積度=k²(高性能化 or 低価格化)

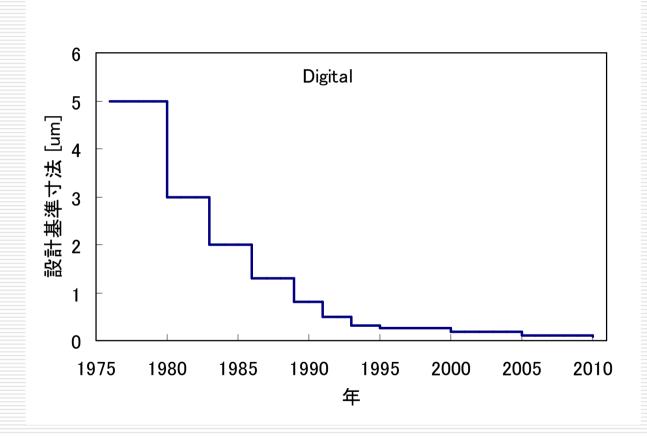

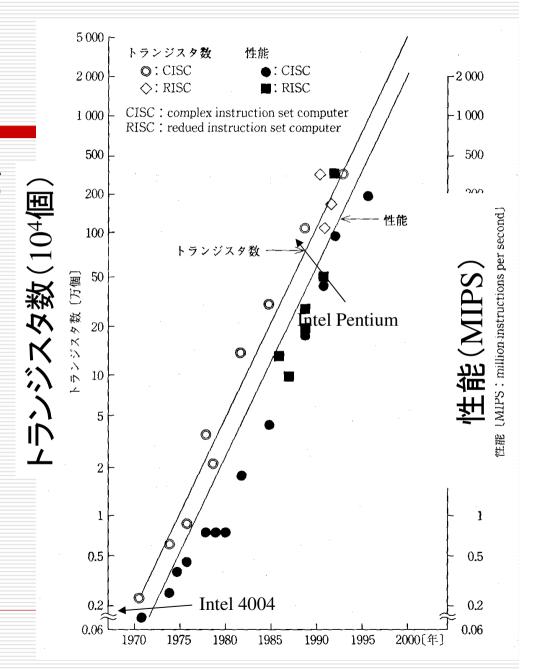

## MOSトランジスタ微細化の歴史

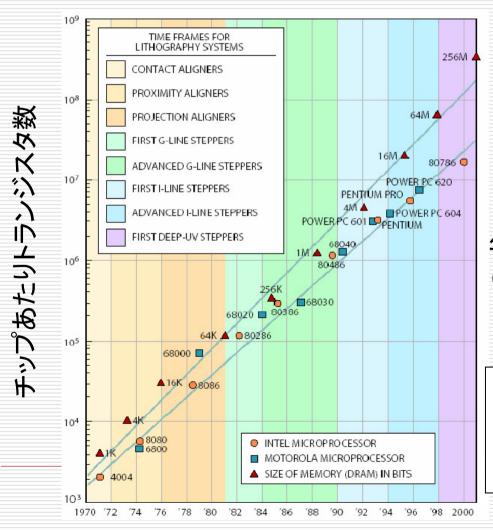

#### Gordon Moore's Law

年率59%=4/3yearsで集積度増大 (「3年で4倍」)

傾き:

プロセッサ: 1.5/years

メモリ: 1.6/years

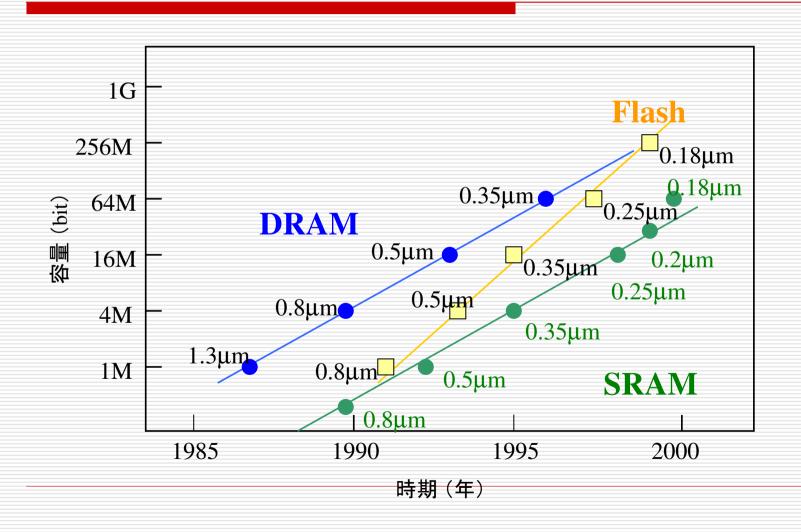

#### Flashメモリ開発動向

### 高性能化の歴史

ロプロセッサの規模と 性能の推移

#### スケーリング則のもたらすもの(その2)

- □ 機能単価:「価格/機能」

- スケーリングにより継続的な機能向上が可能

- 他の産業では見られない特異性

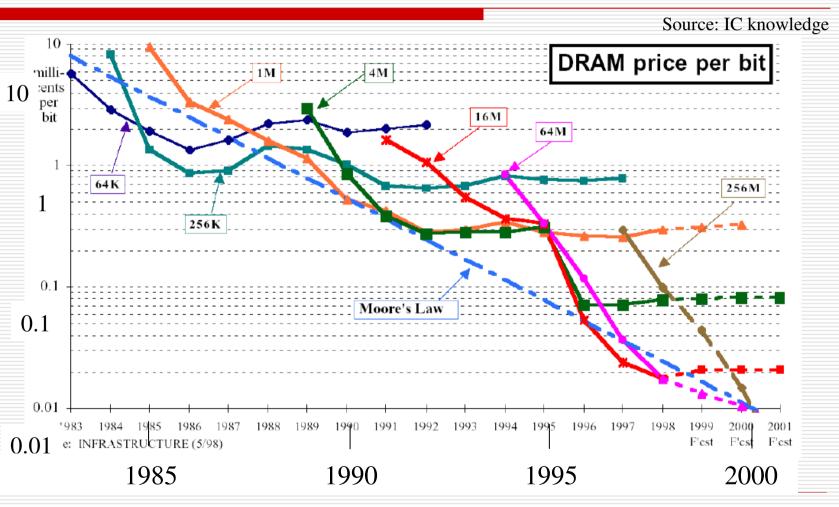

### 低コスト化(その1:DRAMのビット単価)

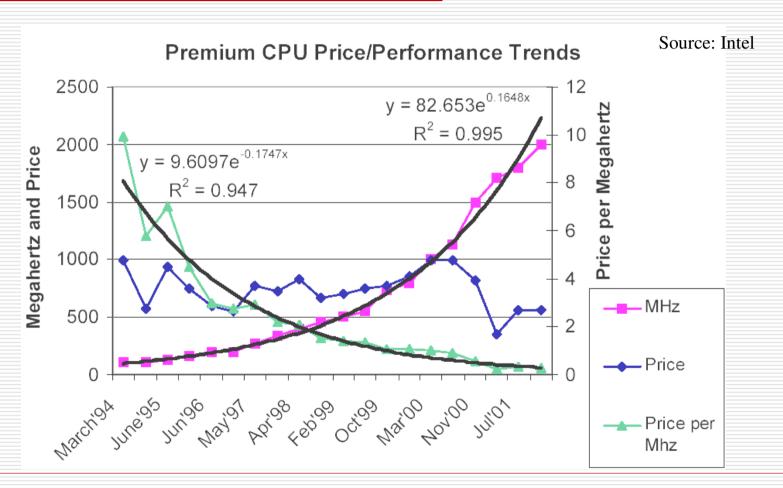

#### 低コスト化 (その2:クロック周波数あたりのプロセッサ価格)

#### 機能単価の低減のみでよいか?

- 口否。

- □「機能飢餓」が必要

- ■「より高性能なものが求められている」状態

- 電子産業は長年この状態にある

- □ シーズとニーズの両立

- ユーザ側:機能飢餓

- メーカ側:スケーリング則によるメリット

### 集積回路の世界の今後は・・・?

- ロ ポイント:

- ■「機能飢餓」は続くのか?

- スケーリングなどの技術的実現性は続くのか?

### Moore's Lawの終わり:技術面

- □ MOSトランジスタの微細化の限界

- MOSトランジスタは原子よりは小さくならない

- L:~0.1um(=100nm)←→ Si原子~1nm

- その他の制限要因

- □ 消費電力の増加(もれ電流)

- □ 回路規模の増大と設計技術の乖離

- L:~0.01um(=10nm)(めどはたっている)

### Moore's Lawの終わり:ニーズ面

- □ 果たして、Moore's Lawによる高性能な集積 回路は必要なのか?

- 例)PCの性能?

- 例)携帯電話の機能?

- 技術的要因だけでは決まらない

- ■・・・これ以上の技術の進歩は必要なのか・・・?

### 集積回路の今後に対する別の見方

- □集積回路の製造・設計技術の成熟

- 高性能な集積回路(MPU, メモリ, ...)

- 低価格な集積回路(性能はそこそこ)

- □ 高性能な集積回路:

- = 最先端の製造技術(工場)

- →(~1000億円以上)

- □ 低価格な集積回路

- 性能はそこそこ。しかし・・・

### 「LEDを点滅させる回路」(1)

□ 普通の設計方法:発振回路

### 「LEDを点滅させる回路」(2)

- □ PCを使ってもできる・・・?

- 可能だが、非現実的・・・か?

```

while(1) {

a = 1;

sleep(1);

a = 0;

sleep(1);

}

```

### マイクロコントローラ(MCU:マイコン)

- □ マイクロコントローラ (MCU)

- CPU+RAM+ROM+周辺回路を1つのチップに

- CPU: 1~100MIPS

- RAM: 1K~10KB

- ROM: 1K~100KB

- Cost: ~100円程度

### 「LEDを点滅させる回路」(3)

- □ 発振回路

- $IC(8p)+C\times1+R\times2=$2$

- □ MCU

- $\blacksquare$  IC(8p)=\$1.5

- 多機能

- □ 点滅速度、点滅パターン などの変更が容易

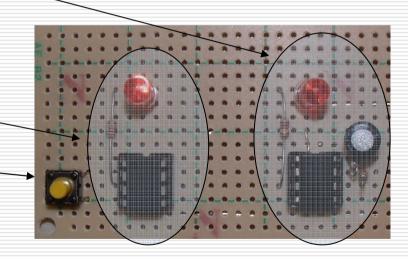

### MCUを使ったLED点滅回路

- □価格・性能の両面で、現実的な選択肢

- □ 性能面では、実は高機能にもできる

- コンピュータを使う!

### これからの情報技術と集積回路

- □「道具」としての集積回路

- 設計技術・製造技術の成熟

- 敷居が下がってきている(学部講義でも扱う!)

- □ 情報技術の実現方法としての集積回路

- パソコンを使ってプログラム:できることは、たかが知れている (パソコンの枠の中だけの世界)

- 面白いもの・作りたいものを実現したいときに、 道具として活用する(実世界とのつながり)

- (そのための準備としての「集積回路工学」)

### 金沢大学のVLSI設計教育

- □ 階層的なカリキュラムによりアルゴリズムから 半導体技術動向までを関連づける

- □ 情報技術関連講義とのリンクをはかり、システムのLSI化を常識のものとする

- □ VDECを活用し、実習による体得を目指す (例:自主課題研究「LSI設計コンテスト」)

#### この講義の予定

第1回: VLSI技術動向 (10/4) 第2回:加算回路(その1)(10/18) □ 第3回:加算回路(その2)(10/25) □ 第4回:減算回路·ALU(11/1) □ 第5回:乗算回路(その1)(11/8) □ 第6回:乗算回路(その2)(11/15) □ 第7回:マイクロプロセッサ(11/22) □ 第8回: SRAM (11/29) □ 第9回: DRAM (12/6) □ 第10回: ROM (12/13) □ 第11回:演算増幅器(12/20) □ 第12回: D/A変換器·A/D変換器 (1/11) □ 第13回:高周波回路(1/17)