戞11夞: 幚廗(6): FPGA傊偺CPU偺幚憰(1)

慜夞奣棯傪愝寁偟偨CPU傪丄弴斣偵嶌偭偰偄偔偙偲偵偟傑偡丅

傑偢崱夞偼丄儗僕僗僞偲墘嶼婍(僨乕僞僷僗)偺傑傢傝傪偮偔偭偰傒傑偡丅

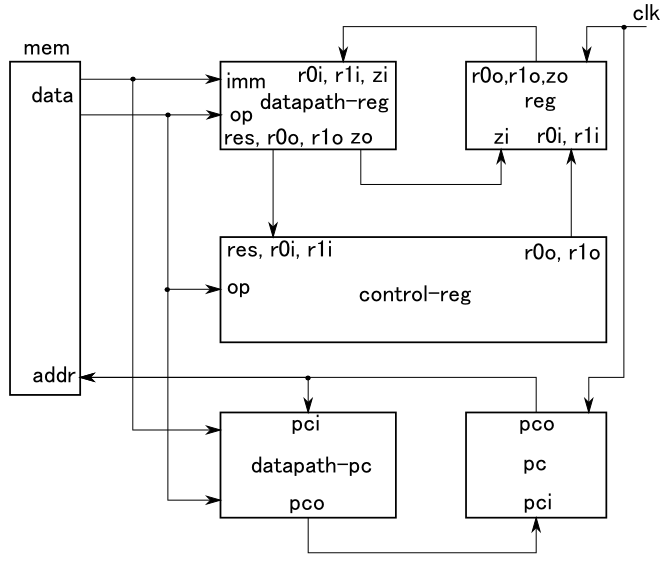

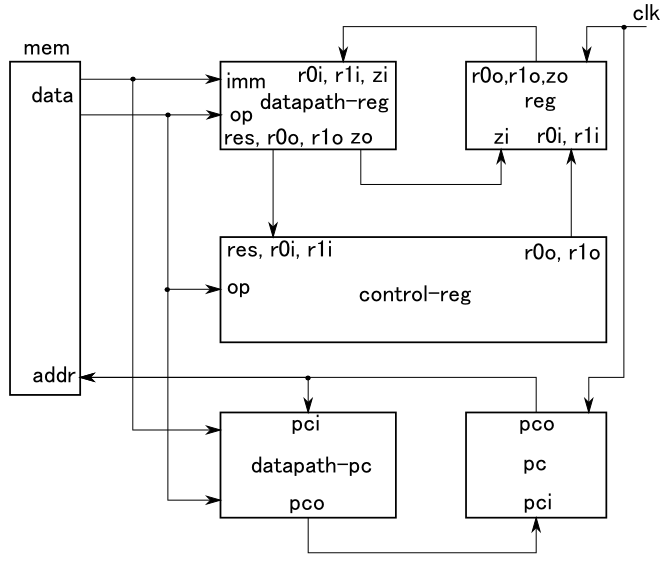

慡懱峔惉

慡懱偺摦嶌偼丄僋儘僢僋clk偵摨婜偟偰(=clk偺棫偪忋偑傝偱)峴偄傑偡丅

庒姳揤壓傝揑偱偡偑丄慡懱峔惉傪埲壓偺傛偆偵偡傞偙偲偵偟偰傒傑偡丅

- datapath_reg: 墘嶼寢壥丒Z僼儔僌偺峏怴偡傞傋偒抣傪惗惉

- reg: 儗僕僗僞丒Z僼儔僌僼儔僌丅clk偵摨婜偟偰丄control_reg偐傜庴偗庢傞

乽r0, r1傪峏怴偡傞傋偒抣乿傪r0, r1偵彂偒崬傓丅

- control_reg: 柦椷(op)偵墳偠偰丄乽r0, r1傪峏怴偡傞傋偒抣乿傪惗惉偡傞丅

- datapath_pc: 僾儘僌儔儉僇僂儞僞(PC)偺峏怴偡傞傋偒抣傪惗惉

- pc: 僾儘僌儔儉僇僂儞僞丅clk偵摨婜偟偰丄datapath_pc偐傜庴偗庢傞

乽pc傪峏怴偡傞傋偒抣乿傪pc偵彂偒崬傓丅梫偼婡擻偼儗僕僗僞偲摨偠丅

- mem: 僾儘僌儔儉奿擺儊儌儕

墘嶼娭學偺僨乕僞僷僗偺愝寁

慜夞偺CPU偺巇條傪傕偲偵丄埲壓偺傛偆側擖弌椡偵懳偟偰

僨乕僞僷僗晹暘(datapath_reg.vhd)傪愝寁偟丄VHDL偱婰弎偟偰傒傑偟傚偆丅

- 擖椡: op(4bit), imm(4bit), r0i(4bit), r1i(4bit), zi(1bit)

仸r0i, r1i偼乽尰嵼偺儗僕僗僞偺抣乿丄 zi偼乽尰嵼偺Z僼儔僌偺抣乿偲偟偰梌偊傞丅

- 弌椡: res(4bit), r0o(4bit), r1o(4bit), zo(1bit)

仸zo偼丄師偵Z僼儔僌偵僙僢僩偝傟傞傋偒抣傪弌椡偡傞

偙傟傜偺擖弌椡傪巊偭偰丄慜夞偺CPU偺柦椷幚峴偺巇條傪枮偨偡傛偆偵

儗僕僗僞偵戙擖偡傞傋偒res偲Z僼儔僌偵僙僢僩偡傞傋偒抣傪媮傔傞

僨乕僞僷僗傪婰弎偟丄僔儈儏儗乕僔儑儞丒幚婡偵傛傝摦嶌傪妋擣偟偰傒傑偟傚偆丅

偨偩偟師夞偺惂屼夞楬偺愝寁偱昁梫偲側傞偨傔丄擖椡偱偁傞r0i, r1i傪

偦偺傑傑弌椡偡傞弌椡r0o, r1o傪偮偗偰偍偒傑偡丅

埲壓丄傂側宍丗

entity datapath_reg is

port( op, imm: in std_logic_vector(3 downto 0);

r0i, r1i: in std_logic_vector(3 downto 0);

zi: in std_logic;

res, r0o, r1o, : out std_logic_vector(3 downto 0);

zo: out std_logic_vector);

end datapath_reg;

architecture Behavioral of datapath_reg is

begin

...

end Behavioral;

偪側傒偵偙偺res偺抣傪丄僋儘僢僋偵偁傢偣偰

柦椷op偵墳偠偰暿搑儗僕僗僞(r0傑偨偼r1)偵曐懚偡傞偙偲偵側傝傑偡丅

僸儞僩

- 偙偺晹暘偼丄僋儘僢僋偑尰傟側偄乽慻傒崌傢偣榑棟夞楬乿偵側傝傑偡丅

- 偙傟偺忋埵偵慡懱峔惉偺datapath_reg_top.vhd傪婰弎偟丄偙傟偺擖弌椡偲偟偰

僾僢僔儏僗僀僢僠(PSW)傗LED丄偝傜偵昁梫偵墳偠偰7僙僌儊儞僩LED梡偺怣崋

(SG, SA)傪掕媊偟丄偦偺拞偱愝寁偟偨cpu傪僀儞僗僞儞僗偲偟偰屇傃弌偟丄

偝傜偵僺儞掕媊(edx001.ucf)傪巊偭偰僐儞僷僀儖偡傞偲傛偄丅

- 擖椡傪僾僢僔儏SW偱梌偊丄寢壥偺res傪LED傗7僙僌儊儞僩LED偱

昞帵偝偣偰摦嶌傪妋擣偡傞偲傛偄偱偟傚偆丅

- 偨偩偟擖椡偺僾僢僔儏僗僀僢僠偑4屄偟偐側偄偺偱丄

op傗imm丄r0i丄r1i丄zi偺懌傝側偄晹暘偼datapath_reg_top.vhd偱

掕悢偲偟偰梌偊傞偺偑尰幚揑偱偟傚偆

僾儘僌儔儉僇僂儞僞偺僨乕僞僷僗偺愝寁

懕偄偰丄僾儘僌儔儉僇僂儞僞(PC)傑傢傝偲Z僼儔僌偺摦嶌傪婰弎偡傞

datapath_pc.vhd傪偮偔偭偰傒傑偡丅

慜夞偺CPU偺巇條傪傕偲偵丄埲壓偺傛偆側擖弌椡偵懳偟偰

僨乕僞僷僗晹暘(datapath_pc.vhd)傪愝寁偟丄VHDL偱婰弎偟偰傒傑偟傚偆丅

- 擖椡: op(4bit), imm(4bit), pci(4bit:乽尰嵼偺PC偺抣乿偲偟偰梌偊傞), zi(1bit)

- 弌椡: pco(4bit:師偵PC偑偲傞傞傋偒抣傪弌椡偡傞)

仸忋偺僽儘僢僋恾偱偼zi偵懳墳偡傞慄偑偁傝傑偣傫偑丄PC偺抣偺寛掕偵偼丄尰嵼偺Z僼儔僌偺抣偑昁梫側偺偱丄捛壛偟偰偍偄偰偔偩偝偄丅

偙傟傜偺擖弌椡偲撪晹曄悢傪巊偭偰丄慜夞偺CPU偺柦椷幚峴偺巇條傪枮偨偡傛偆偵

PC偵戙擖偡傞傋偒抣pco傪偒傔傞僨乕僞僷僗傪婰弎偟偰傒傑偟傚偆丅

埲壓丄傂側宍丗

entity datapath_pc is

port( op, imm, pci: in std_logic_vector(3 downto 0);

zi: in std_logic;

pco: out std_logic_vector(3 downto 0));

end datapath_pc;

architecture Behavioral of datapath_pc is

begin

...

end Behavioral;

僸儞僩

- 偙偺晹暘偼丄僋儘僢僋偑尰傟側偄乽慻傒崌傢偣榑棟夞楬乿偵側傝傑偡丅

- 偙傟偺忋埵偵慡懱峔惉偺datapath_pc_top.vhd傪婰弎偟丄偙傟偺擖弌椡偲偟偰

僾僢僔儏僗僀僢僠(PSW)傗LED丄偝傜偵昁梫偵墳偠偰7僙僌儊儞僩LED梡偺怣崋

(SG, SA)傪掕媊偟丄偦偺拞偱愝寁偟偨cpu傪僀儞僗僞儞僗偲偟偰屇傃弌偟丄

偝傜偵僺儞掕媊(edx001.ucf)傪巊偭偰僐儞僷僀儖偡傞偲傛偄丅

- 擖椡傪僾僢僔儏SW偱梌偊丄寢壥偺pco傪LED傗7僙僌儊儞僩LED偱

昞帵偝偣偰摦嶌傪妋擣偡傞偲傛偄偱偟傚偆丅

- 偨偩偟擖椡偺僾僢僔儏僗僀僢僠偑4屄偟偐側偄偺偱丄

op傗imm丄pci偺懌傝側偄晹暘偼datapath_reg_top.vhd偱

掕悢偲偟偰梌偊傞偺偑尰幚揑偱偟傚偆

儊儌儕偺愝寁

崱夞偼儊儌儕偼撉傒弌偟愱梡偱偡偐傜丄僨僐乕僟偲摨條偵

擖椡偲偟偰梌偊傞傾僪儗僗addr偵墳偠偰丄偦偙偺抣data傪弌椡偡傞

夞楬丄偲偟偰愝寁偡傟偽傛偄偙偲偵側傝傑偡丅

椺偊偽僥僗僩梡偵師偺傛偆側乽僾儘僌儔儉乿傪曐帩偡傞儊儌儕傪愝寁偟偰傒傑偟傚偆丅

| 傾僪儗僗 | 撪梕 | 柦椷 |

| 0 | 0000 0001 | mov 1, r0 |

| 1 | 0010 0010 | add r0, 2, r0 |

| 2 | 0110 0010 | jmp 2 |

埲壓丄傂側宍丗

entity mem is

port( addr: in std_logic_vector(3 downto 0);

data: out std_logic_vector(7 downto 0));

end mem;

architecture Behavioral of mem is

begin

...

end Behavioral;

栠傞