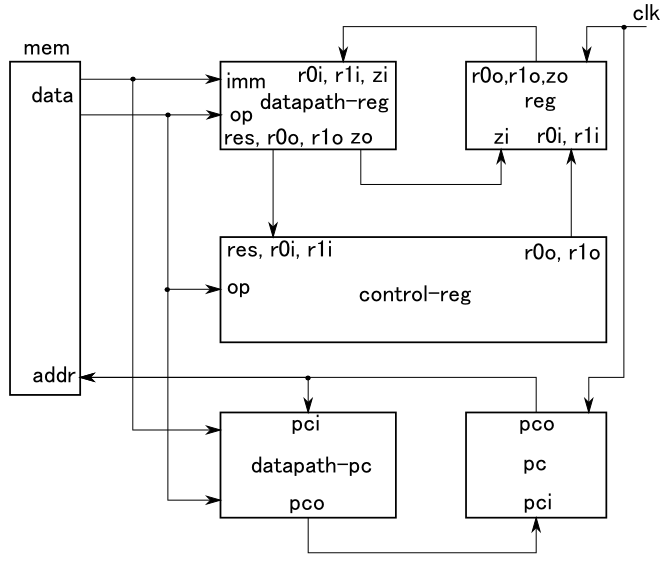

第12回: 実習(7): FPGAへのCPUの実装(2)

全体構成と制御回路の設計

- datapath_reg: 演算結果・Zフラグの更新するべき値を生成(設計済み)

- reg: レジスタ・Zフラグフラグ。clkに同期して、control_regから受け取る

「r0, r1を更新するべき値」をr0, r1に書き込む。

- control_reg: 命令(op)に応じて、「r0, r1を更新するべき値」を生成する。

- datapath_pc: プログラムカウンタ(PC)の更新するべき値を生成(設計済み)

- pc: プログラムカウンタ。clkに同期して、datapath_pcから受け取る

「pcを更新するべき値」をpcに書き込む。要は機能はレジスタと同じ。

- mem: プログラム格納メモリ(設計済み)

以下では、未設計の部分を順につくっていき、

適宜シミュレーションや実機で動作確認をしてみましょう。

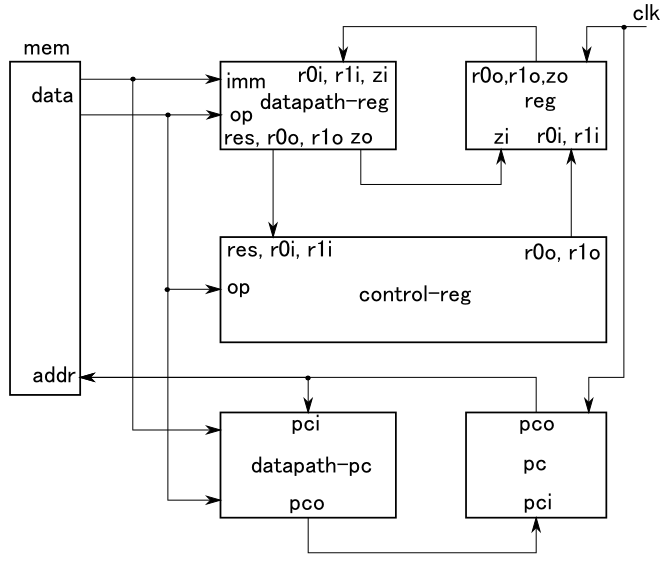

レジスタとプログラムカウンタ

reg, pcは、一般的なレジスタ(D-FF)と同様の動作ですので、

レジスタの記述を参考にVHDL記述します。

制御回路の設計:レジスタの制御

命令(op)に応じて、datapath_regで生成された演算結果(res)を、

r0またはr1に書き込むように「r0, r1を更新するべき値」を生成します。

例えば、op="0000"(mov imm, r0)では、datapath_regでres=immとなっていますが、

これを書き込む先はr0ですからr0o=resとなり、

またr1は変更しませんから、r1の現在の値であるr1iを、そのままr1o=r1iとして

出力すればよいことになります。

他にも同様に、例えばop="0011"(add r0, imm, r1)ならば、r0o=r0i, r1o=resとなります。

戻る