戞3夞: 幚廗(1): FPGA傊偺榑棟夞楬偺幚憰

崱夞偼丄VHDL傪梡偄偰婰弎偟偨夞楬傪丄幚嵺偵摦嶌偡傞

榑棟夞楬偲偟偰摦嶌傪偝偣偰傒傑偟傚偆丅

偙偺墘廗偱偼丄愇愳崅愱僆儕僕僫儖儃乕僪傪巊偄傑偡丅

偙偺憰抲偼丄愝寁偟偨榑棟夞楬傪帺桼偵彂偒崬傓偙偲偑偱偒傞

FPGA (Field Programmable Gate Array)偲屇偽傟傞LSI偺堦庬偱丄

Xilinx幮偺Spartan6 (XC6SLX16)偲偄偆LSI偑搵嵹偝傟偰偄偰丄

偝傜偵擖椡丄弌椡偲偟偰巊偆僗僀僢僠傗LED側偳傪

僒僽儃乕僪偲偟偰梡搑偵崌傢偣偰嵎偟懼偊傞偙偲偑偱偒傑偡丅

傑偨愝寁偟偨榑棟夞楬偺忣曬偼丄PC偐傜USB愙懕偺彂偒崬傒婍偱

彂偒崬傓偙偲偑偱偒傑偡丅

崱夞偺墘廗偱偼丄"Sub3"偲偄偆儔儀儖偺揬偭偰偁傞丄

7僙僌儊儞僩LED偑嵹偭偰偄傞僒僽儃乕僪傪偝偟偰巊偄傑偡丅

楙廗: NOT僎乕僩

僾儘僕僃僋僩偺嶌惉

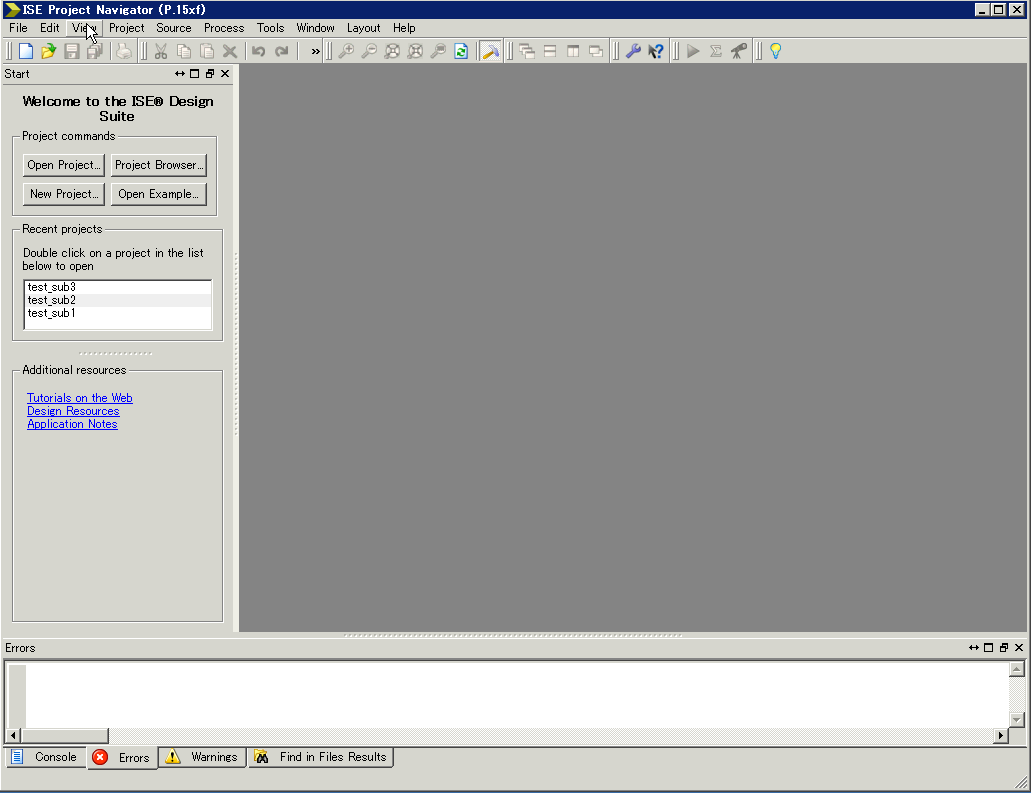

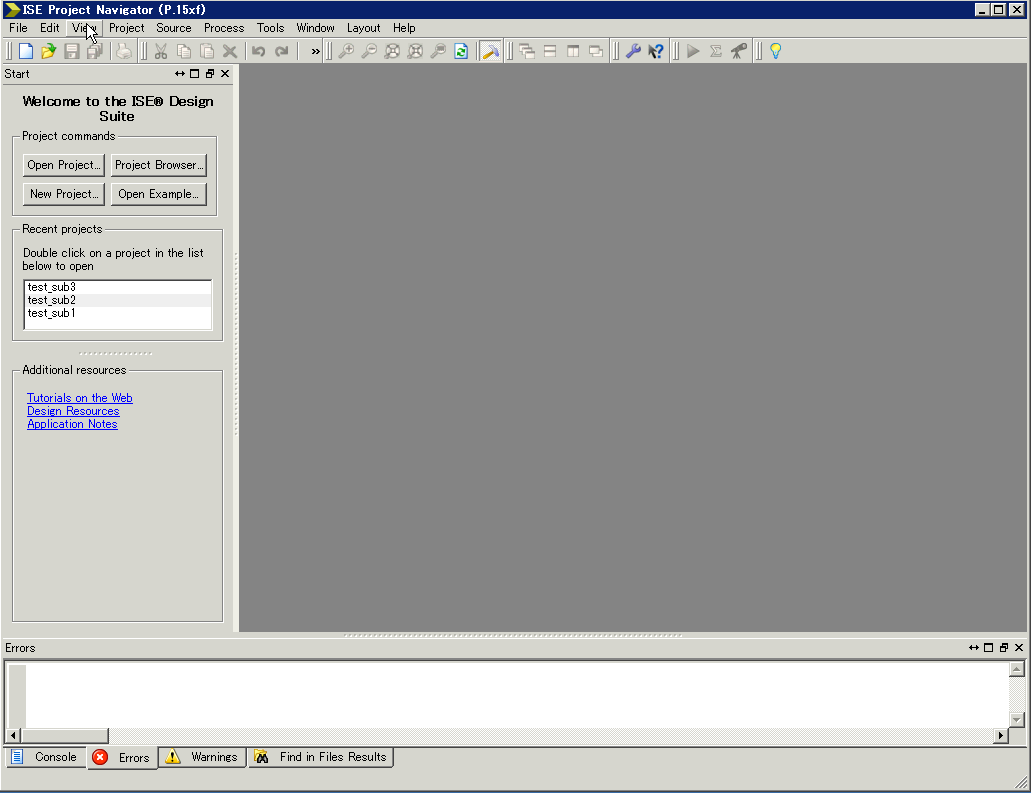

PC傪婲摦屻丄僨僗僋僩僢僾偺Project Navigator偺傾僀僐儞丄

傑偨偼僗僞乕僩儊僯儏乕偐傜丄

榑棟愝寁梡偺僜僼僩僂僄傾Xilinx ISE Project Navigator傪婲摦偟傑偡丅

偙傫側姶偠偺夋柺偑弌傞偼偢偱偡丅

偙傟偐傜愝寁偟偰偄偔榑棟夞楬偼丄乽僾儘僕僃僋僩乿偲偄偆扨埵偱

埖偄傑偡丅

憗懍丄怴偟偄僾儘僕僃僋僩傪嶌偭偰傒傑偟傚偆丅

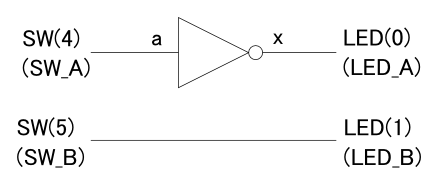

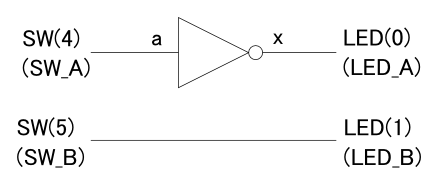

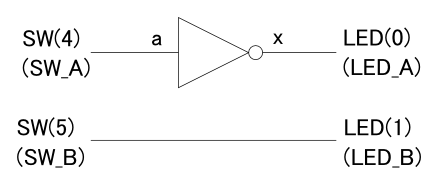

傑偢偼庤巒傔偵丄NOT僎乕僩(僀儞僶乕僞)1屄傪丄擖椡偵僗僀僢僠A(SW_A)丄

弌椡偵LED_A傪偮側偄偱傒傞偙偲偵偟傑偡丅

偮偄偱偵丄傕偆1屄偺僗僀僢僠B(SW_B)傪丄偦偺傑傑LED_B偵偮側偄偩夞楬傕

嶌偭偰傒傞偙偲偵偟傑偡丅

偮傑傝崱夞偮偔傞夞楬偼丄偙傫側姶偠偵側傝傑偡丅

側偍懠偺儃乕僪偲偺屳姺惈偺搒崌忋丄

僗僀僢僠A, B偼丄偦傟偧傟SW(4), SW(5)丄

LED_A, LED_B偼丄偦傟偧傟LED(0), LED(1)偲偄偆柤慜偵側傝傑偡丅

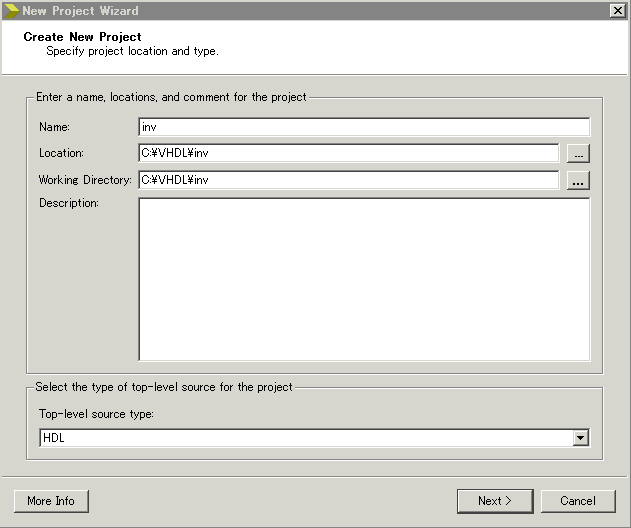

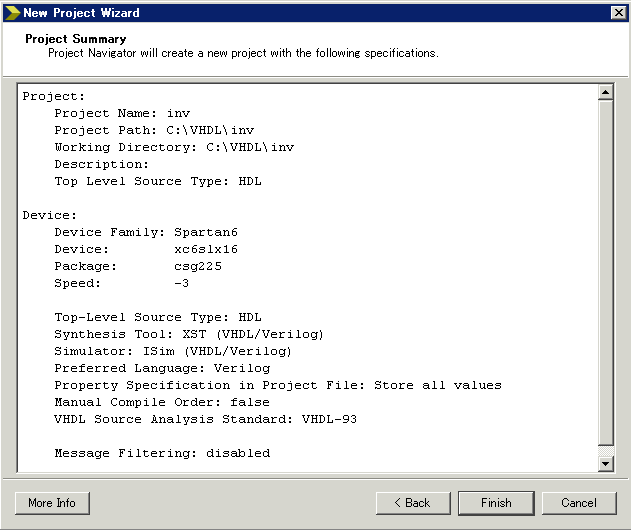

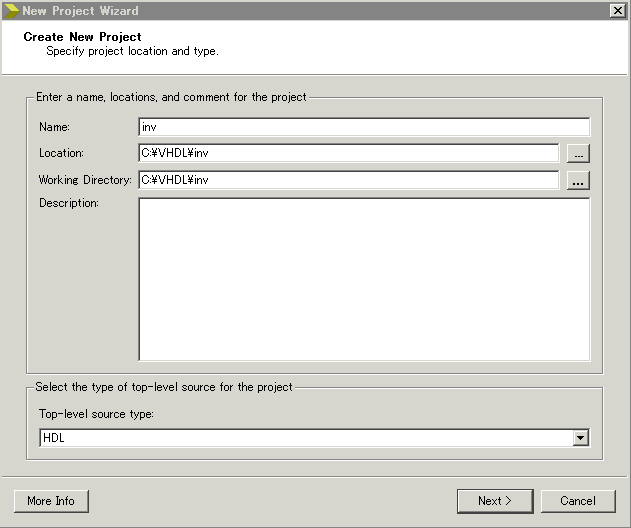

File仺New Project偱丄怴偟偄僾儘僕僃僋僩偺嶌惉傪奐巒偟傑偡丅

僾儘僕僃僋僩偺柤慜傗僼傽僀儖傪抲偔僨傿儗僋僩儕柤側偳傪

擖椡偟傑偡丅

偙偺椺偱偼丄僾儘僕僃僋僩偺柤慜偵inv偲偟偰偄傑偡丅

僼傽僀儖傪抲偔僨傿儗僋僩儕偼丄

偲傝偁偊偢偼帺暘偺PC撪("C:亸"側偳)偵揔摉側僼僅儖僟("VHDL"側偳)傪偮偔傝丄

偦偺拞偵嶌偭偰偄偭偰偔偩偝偄丅

仸偨偩偟墘廗廔椆屻偵PC傪僔儍僢僩僟僂儞偡傞慜偵丄墘廗偱嶌偭偨偙傟傜偺僼傽僀儖傪僼傽僀儖僒乕僶偵曐懚偟偰偍偔偺傪朰傟偢偵!

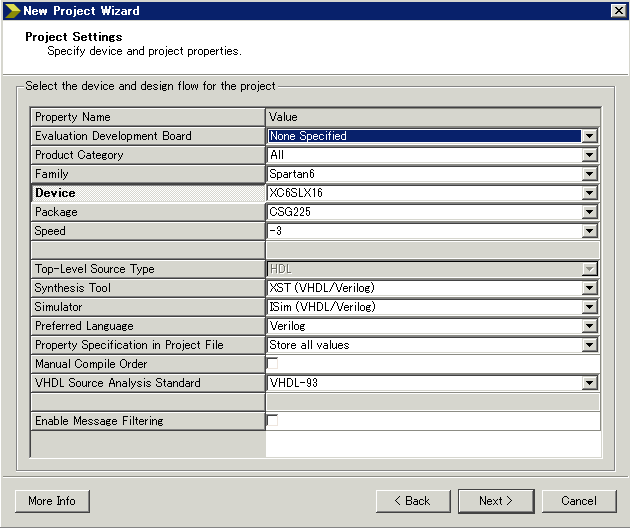

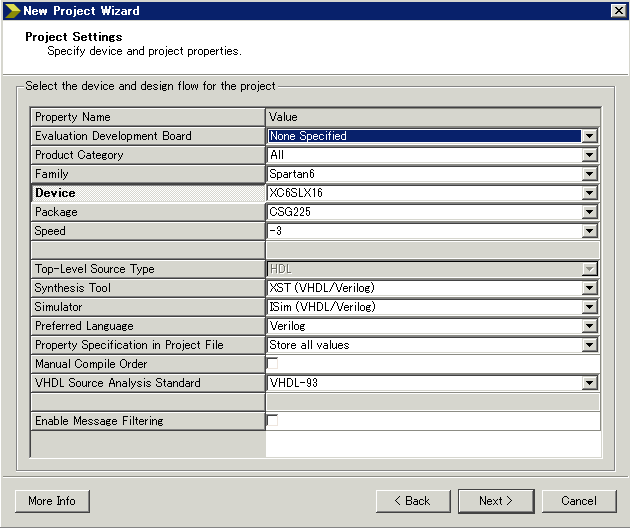

懕偄偰丄崱夞巊偆儃乕僪偵嵹偭偰偄傞丄愝寁偟偨榑棟夞楬傪

彂偒崬傓FPGA偲偟偰Spartan6 (XC6SLX16)傪慖傃傑偡丅

偦偺傎偐偵傕丄偙偺XC6SLX16偺僷僢働乕僕丄僺儞悢側偳偺忣曬傪

慖傇昁梫偑偁傝傑偡偺偱丄仾偙偺恾偺捠傝偵慖傫偱偍偒傑偡丅

摿偵丄Device偺偲偙傠偱"XC6SLX16"傪慖傫偱偄傞偐拲堄丅

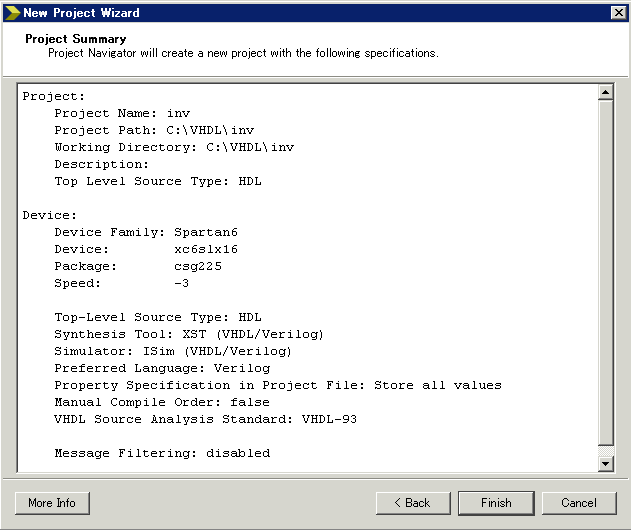

仾慖戰偑廔傢偭偨傜丄Next傪墴偡偲丄偲傝偁偊偢僾儘僕僃僋僩偑嶌惉偝傟傑偡丅

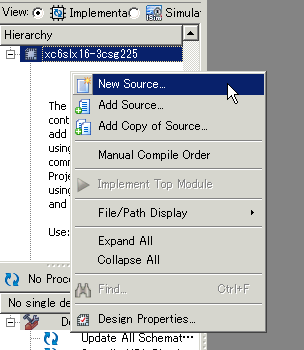

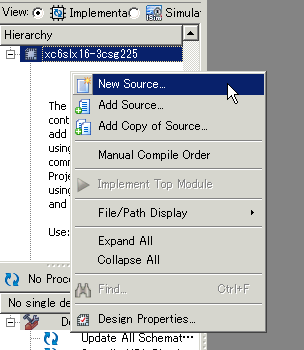

懕偄偰丄愝寁偡傞夞楬傪婰弎偡傞VHDL僼傽僀儖傪嶌惉偟傑偡丅

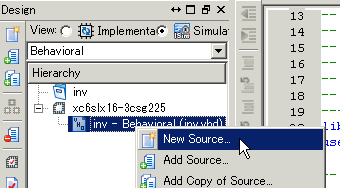

仾崱夞偼丄怴偟偄僼傽僀儖傪嶌傝傑偡偺偱丄

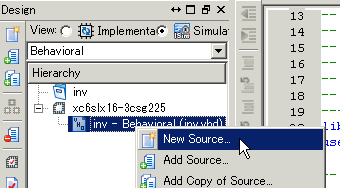

偙偙偱怴偟偄僼傽僀儖傪嶌傞偨傔偵丄

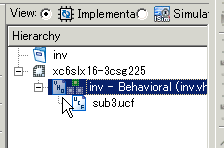

嵍忋偺曽偺FPGA儅乕僋(xc6slx16-...偲彂偄偰偁傞)傪塃僋儕僢僋偟偰

New Source傪慖傃傑偡丅

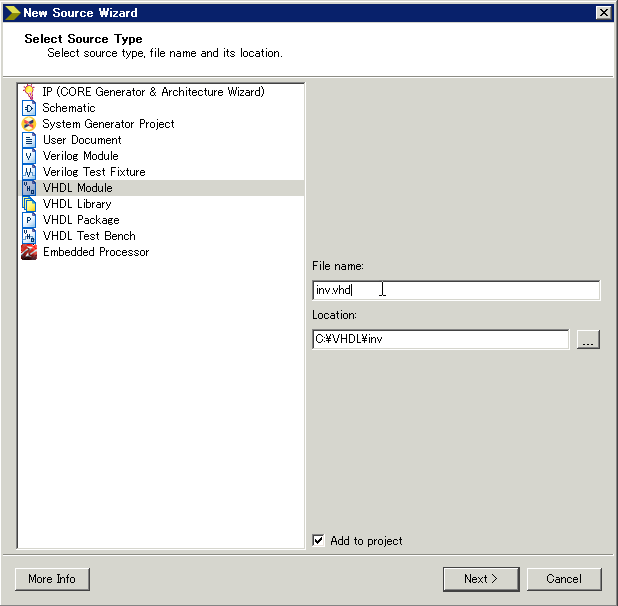

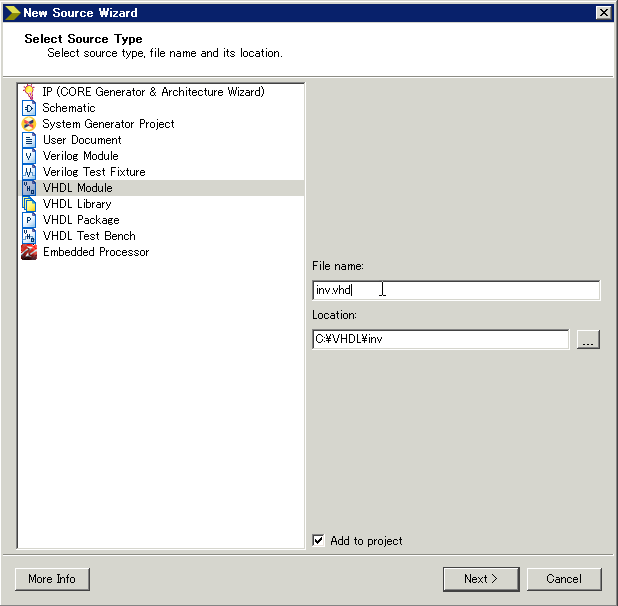

怴偟偔嶌惉偡傞僼傽僀儖偺庬椶偲僼傽僀儖柤傪擖椡偟傑偡丅

崱夞偼丄VHDL偱夞楬傪愝寁偟傑偡偺偱VHDL Module傪慖傃丄

僼傽僀儖柤偼丄inv.vhd偲偟偰偍偒傑偡丅

Next> 儃僞儞偱師傊丅

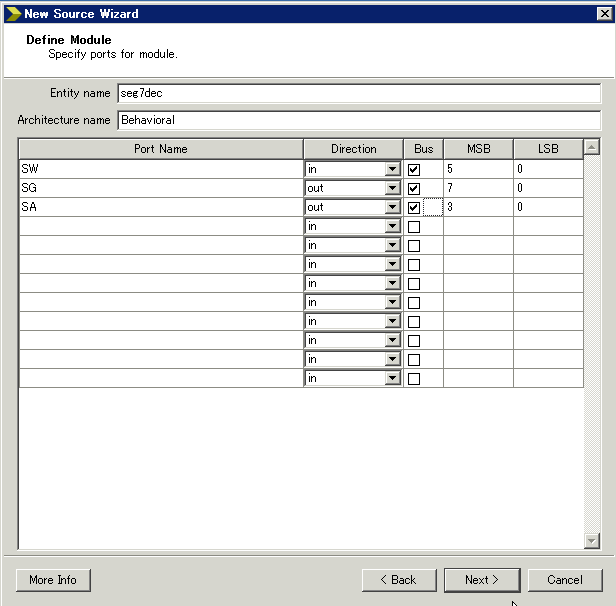

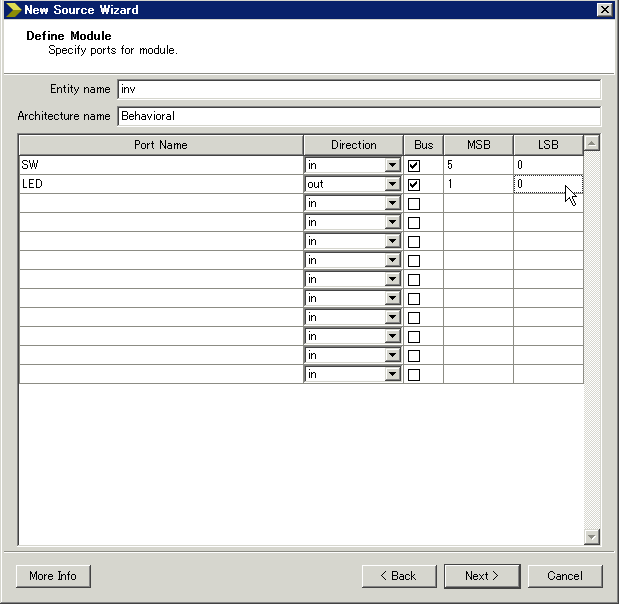

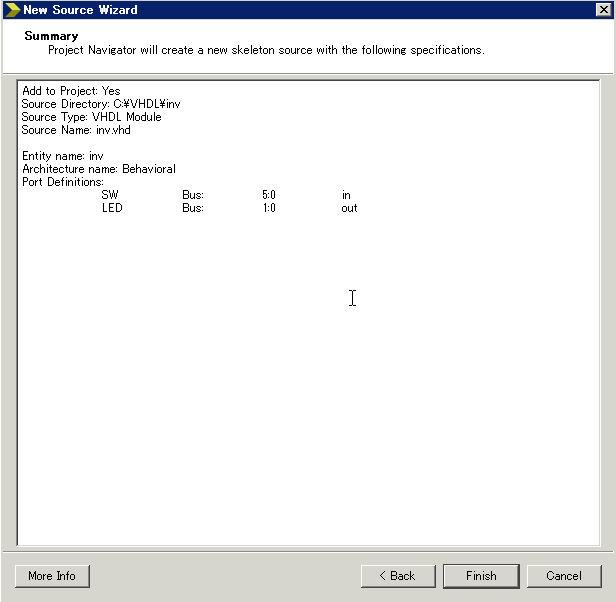

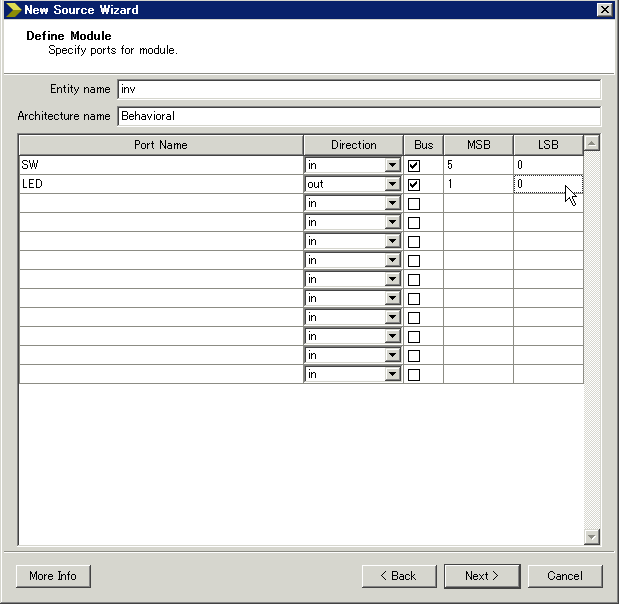

懕偄偰丄偙偺夞楬慡懱偺擖椡丒弌椡傪掕媊偟傑偡丅

偙偺椺偱偼丄擖椡(in)偲偟偰SW偲偄偆柤慜偺抂巕偲丄

弌椡(out)偲偟偰LED偲偄偆柤慜偺抂巕傪巊偆偙偲傪巜掕偟偰偄傑偡丅

側偍僒僽儃乕僪忋偵偼僗僀僢僠偑6屄偁傝傑偡(偨偩偟崱夞巊偆偺偼2屄偩偗)丅

偙偺傛偆偵暋悢偺怣崋傪傑偲傔偰攝楍偺傛偆偵埖偆偲偒偵偼丄

仾偺傛偆偵"Bus"偵僠僃僢僋傪擖傟丄偦偺揧偊帤傪MSB(嵟戝抣)偲LSB(嵟彫抣:捠忢偼0)偵

彂偄偰偍偒傑偡丅

偙偺椺偱偼丄幚嵺偵偼SW(0)乣SW(5)偺6杮偲LED(0)乣LED(1)偺2杮偑巊傢傟傑偡丅

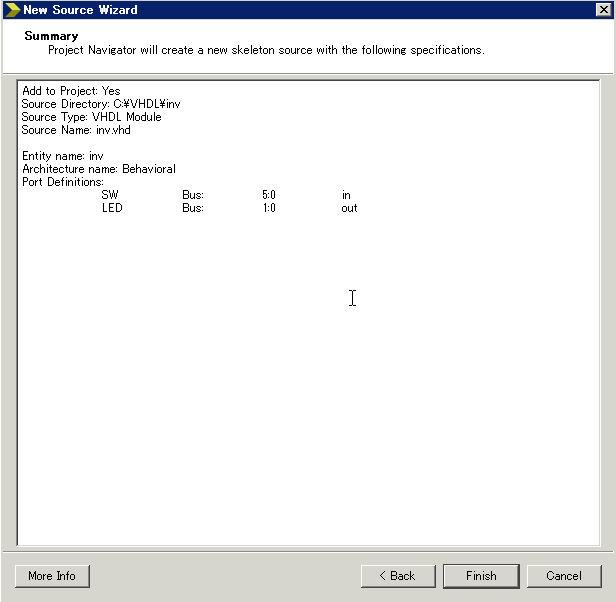

偙傟偱丄偙傟偐傜愝寁偡傞夞楬偺VHDL僼傽僀儖偺掕媊偑偡傒傑偟偨偺偱丄

偙偙偱妋擣偟丄Finish儃僞儞傪墴偟傑偡丅

偙傟偱丄怴偟偔夞楬偺愝寁傪偼偠傔傞弨旛偑惍偄傑偟偨丅

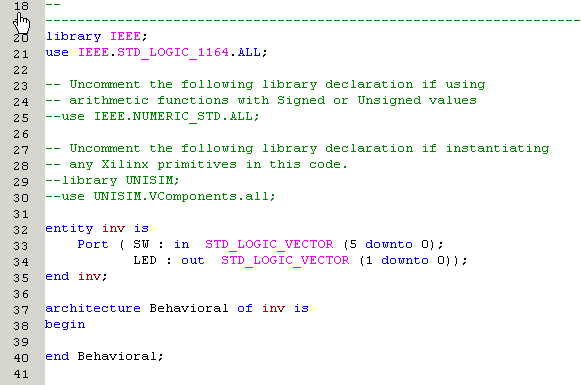

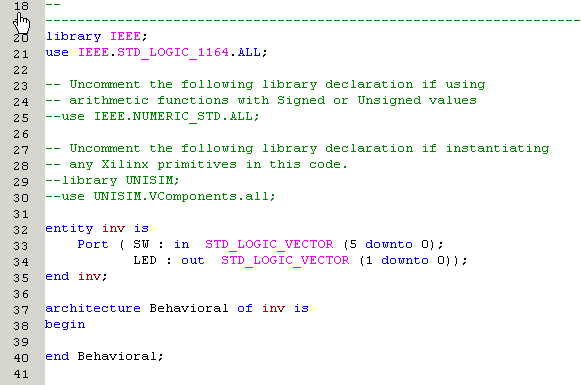

仾夋柺撪偺inv.vhd僞僽傪慖傫偱傒傞偲丄

偄傑偐傜愝寁偡傞夞楬inv傪婰弎偡傞VHDL僼傽僀儖偱丄

昁梫側売強(偍傑偠側偄傗丄entity婰弎側偳)偑

婛偵婰擖偝傟偰偄傞偙偲偑傢偐傝傑偡丅

偙傟偼丄僾儘僕僃僋僩偺嶌惉帪偵丄巊偆擖弌椡偺柤慜側偳傪

巜掕偟偰偄偨偺偱丄偦傟偵偁傢偣偰丄VHDL偺偍寛傑傝偺婰弎偺晹暘傪

悧宍(僥儞僾儗乕僩)偲偟偰帺摦揑偵嶌惉偝傟偨偺偱偟偨丅

曋棙偱偡偹丅

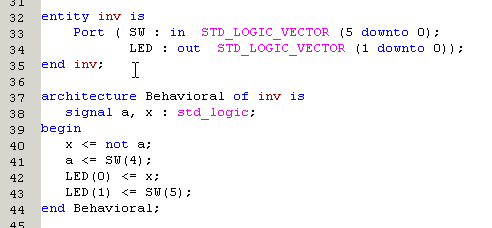

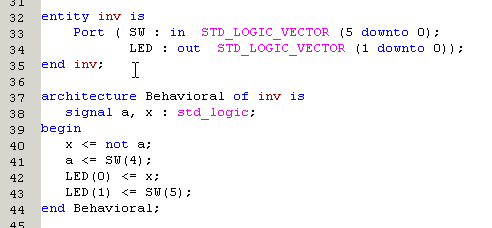

偱偼丄杮戣偱偁傞NOT僎乕僩傪丄仾偙偺傛偆偵婰擖傪偟偰偍偒傑偟傚偆丅

拲栚偟偰偍偔傋偒揰傪偄偔偮偐丅

- NOT僎乕僩偦偺傕偺偼丄40峴栚偵擖椡a偲弌椡x偺娭學偲偟偰掕媊偟偰偄傑偡丅

- 偙偺擖椡a偲弌椡x偼丄夞楬慡懱(儃乕僪)偺擖弌椡偵偼側偄怣崋側偺偱丄

38峴栚偵signal偲偟偰愰尵偟偰偄傑偡丅

- 夞楬慡懱(儃乕僪)偺擖椡偱偁傞僗僀僢僠A(SW(4)偲

弌椡偱偁傞LED A(LED(0))偼丄偦傟偧傟撪晹偺怣崋a, x偲

41, 42峴栚偱愙懕偡傞傛偆婰弎偟偰偄傑偡丅

仸傑傢傝偔偳偄婰弎偵巚偊傞偐傕偟傟傑偣傫偑丄

屻乆偺偨傔偵偙偺傛偆側婰弎偺偟偐偨偵側傟偰偍偔偲傛偄偱偡丅

- 傕偆1偮偺僗僀僢僠B(SW(5))偲LED B(LED(1))偼丄

柺搢側偺偱43峴栚偺傛偆偵偦偺傑傑偮側偖傛偆偵婰弎偟偰偄傑偡丅

(偑丄杮棃偼signal傪愰尵偟偰婰弎偡傋偒偱偡)

僔儈儏儗乕僔儑儞

師偵丄愝寁偟偨夞楬傪丄僥僗僩儀儞僠(専徹偺偨傔偵梌偊傞擖椡怣崋)傪

梡偄偰僔儈儏儗乕僔儑儞偟丄惓偟偔摦嶌偡傞偐傪専徹偟偰傒傞偙偲偵偟傑偡丅

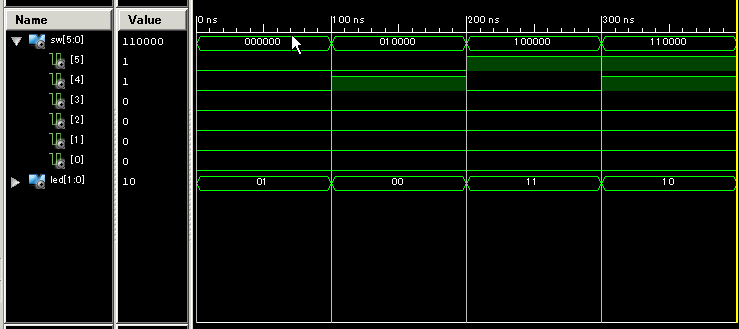

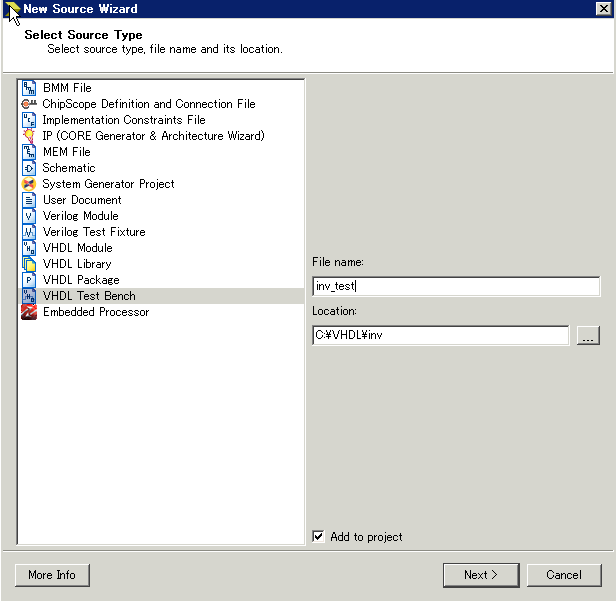

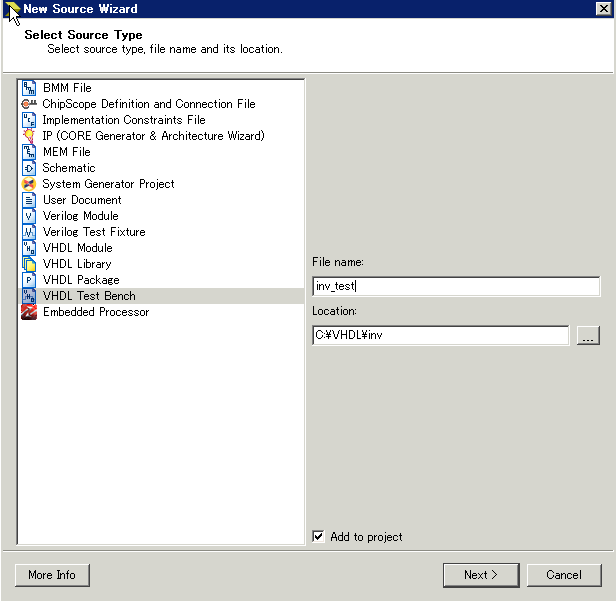

僥僗僩儀儞僠傪婰弎偡傞VHDL僼傽僀儖傪怴婯偵嶌惉偡傞偨傔丄

嵍忋偺曽偺丄View:偺偲偙傠偱Simulation傪慖戰偟丄

愝寁偟偰偄傞夞楬偺僼傽僀儖偱偁傞inv傪

塃僋儕僢僋偟丄New Source傪慖傃傑偡丅

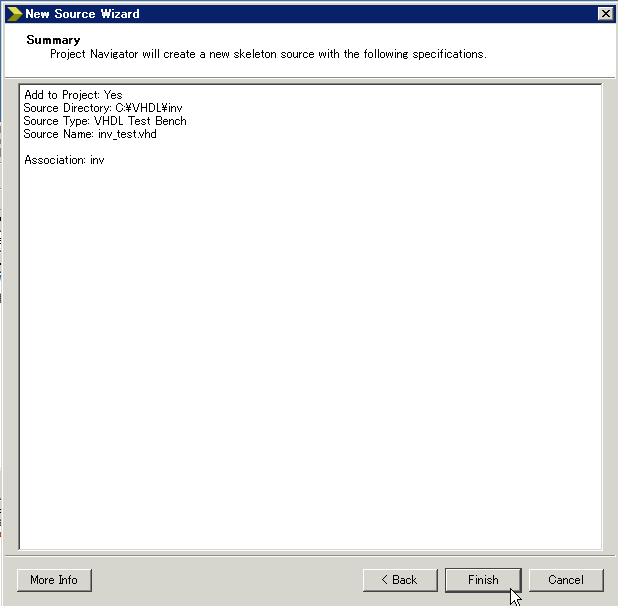

嶌惉偡傞僼傽僀儖偲偟偰丄VHDL TestBench丄僼傽僀儖柤傪inv_test偲偟偰丄Next丅

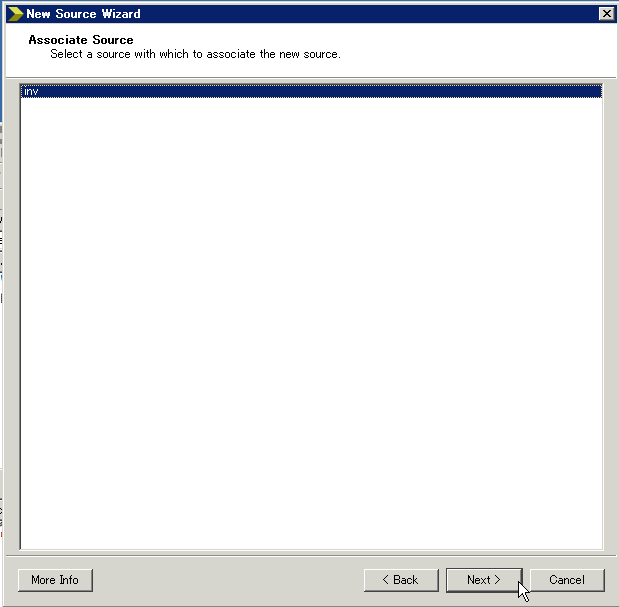

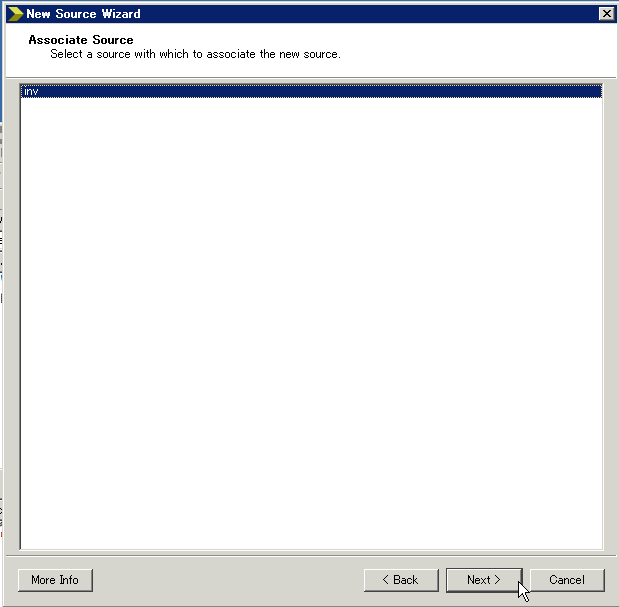

偄傑偐傜嶌惉偟傛偆偲偡傞僥僗僩儀儞僠偑丄偳偺夞楬傪懳徾偲偡傞傕偺偐丄

傪慖傇夋柺偵側傝傑偡偑丄崱夞偼inv偟偐側偄偺偱丄偦偺傑傑Next丅

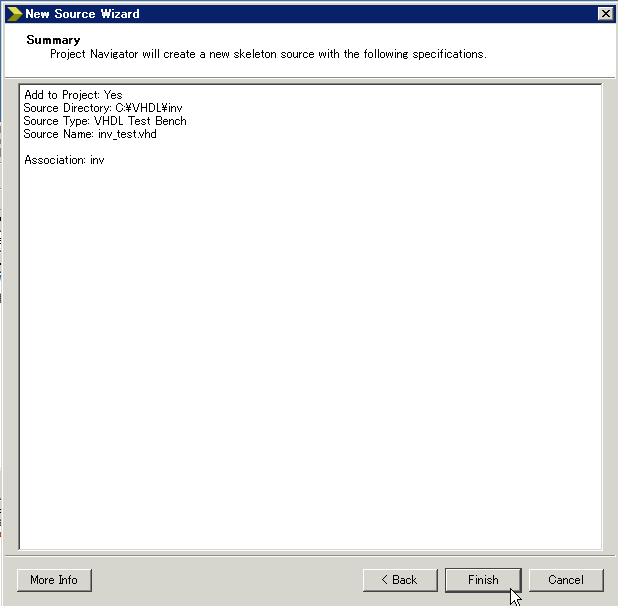

僥僗僩儀儞僠偺VHDL僼傽僀儖傪嶌惉偡傞弨旛偑惍偭偨偺偱丄Finish丅

僥僗僩儀儞僠僼傽僀儖inv_test.vhd偑奐偐傟偰偄傞忬懺偵

側偭偰偄傞偼偢偱偡偑丄偝偒傎偳偺夞楬杮懱偺VHDL僼傽僀儖偺偲偒偲

摨條偵丄偍傑偠側偄側偳偺昁梫売強偼丄偡偱偵婰擖偝傟偨忬懺偵

側偭偰偄傑偡丅曋棙偱偡偹丅

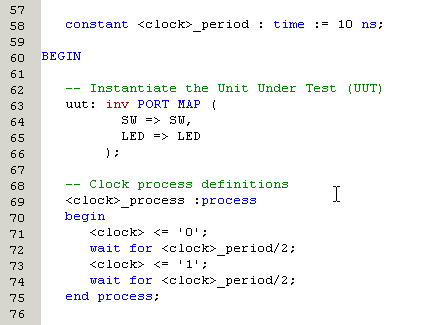

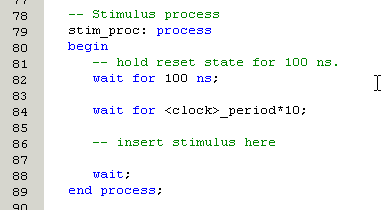

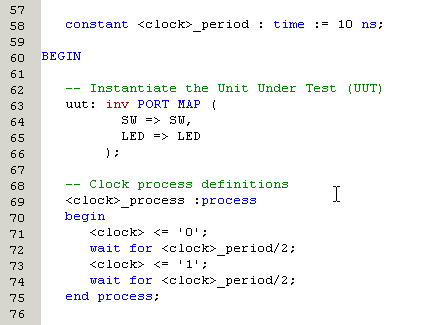

偨偩偟梋寁側偍悽榖傕偁偭偰丄師夞偺墘廗偱埖偆弴彉夞楬岦偗偵丄

僋儘僢僋怣崋娭學偺婰弎傕丄帺摦偱擖偭偰偟傑偄傑偡丅

偟偐偟崱夞偺夞楬偱偼僋儘僢僋怣崋偼巊偄傑偣傫偺偱丄

偙傟傜偺婰弎偼僐儊儞僩傾僂僩(峴摢偵乽--乿傪偮偗傞)偡傞偐

嶍彍偟偰偍偒傑偟傚偆丅

仾偺椺偱偼69乣75峴栚偑奩摉偟傑偡偺偱丄偙傟偲摨條偺婰弎傪尒偮偗偰

僐儊儞僩傾僂僩偡傞偐嶍彍偟偰偍偄偰偔偩偝偄丅

僔儈儏儗乕僔儑儞偱偼丄夞楬偵怣崋傪梌偊丄偦傟偵懳偟偰弌偰偔傞

弌椡傪娤嶡偟偰丄偦傟偑強朷偺傕偺偱偁傞偐傪妋擣偡傞傢偗偱偡偑丄

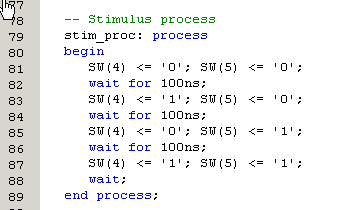

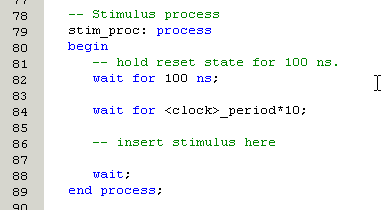

夞楬偵梌偊傞怣崋偼丄乽stim_proc乿埲崀(偙偺椺偱偼80峴栚偐傜)偵婰弎偟傑偡丅

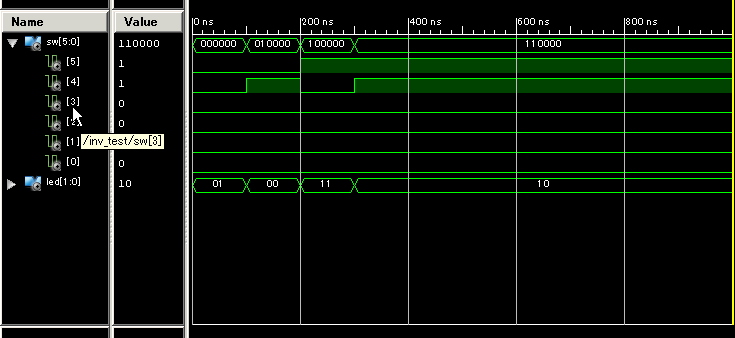

崱夞偼擖椡偑SW(4), SW(5)偺2偮偱丄偦傟偧傟0 or 1偺抣偱偡偺偱丄

偤傫傇偱4捠傝偺慻傒崌傢偣偑偁傝傑偡丅

偙傟偖傜偄偺婯柾偱偁傟偽丄慡偰偺慻傒崌傢偣傪梌偊偰妋擣偡傞偺偑傛偄偱偟傚偆丅

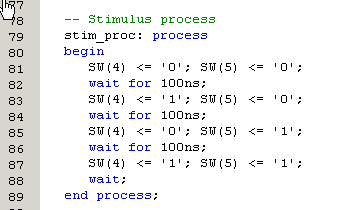

偲偄偆傢偗偱丄仾偺傛偆偵婰弎偟偰傒傑偡丅

偙傟偼丄81峴栚偐傜弴偵埲壓偺傛偆側怣崋傪梌偊傞婰弎偵側偭偰偄傞偙偲傪

(側傫偲側偔偱傛偄偺偱)棟夝偟偰偍偒傑偟傚偆丅

- SW(4)="0", SW(5)="0"傪梌偊傞

- 彮偟(100ns)懸偮

- SW(4)="1", SW(5)="0"傪梌偊傞

- 彮偟(100ns)懸偮

- SW(4)="0", SW(5)="1"傪梌偊傞

- 彮偟(100ns)懸偮

- SW(4)="1", SW(5)="1"傪梌偊傞

- 彮偟(100ns)懸偮

偙傟偱僥僗僩儀儞僠偺婰弎偑廔傢傝傑偟偨偺偱丄

僥僗僩儀儞僠偱偁傞inv_test傪慖戰偟偨忬懺偱丄

壓偺Processes夋柺撪偺Simulate Behavioral Model傪

塃僋儕僢僋偟丄Run傪慖傫偱僔儈儏儗乕僔儑儞傪奐巒偟傑偡丅

偙偺偲偒丄婰弎偟偨夞楬傗僥僗僩儀儞僠摍偵婰弎儈僗偑偁傞偲

僄儔乕儊僢僙乕僕偑昞帵偝傟傑偡偺偱丄僄儔乕儊僢僙乕僕傪嶲徠偟側偑傜廋惓偟傑偡丅

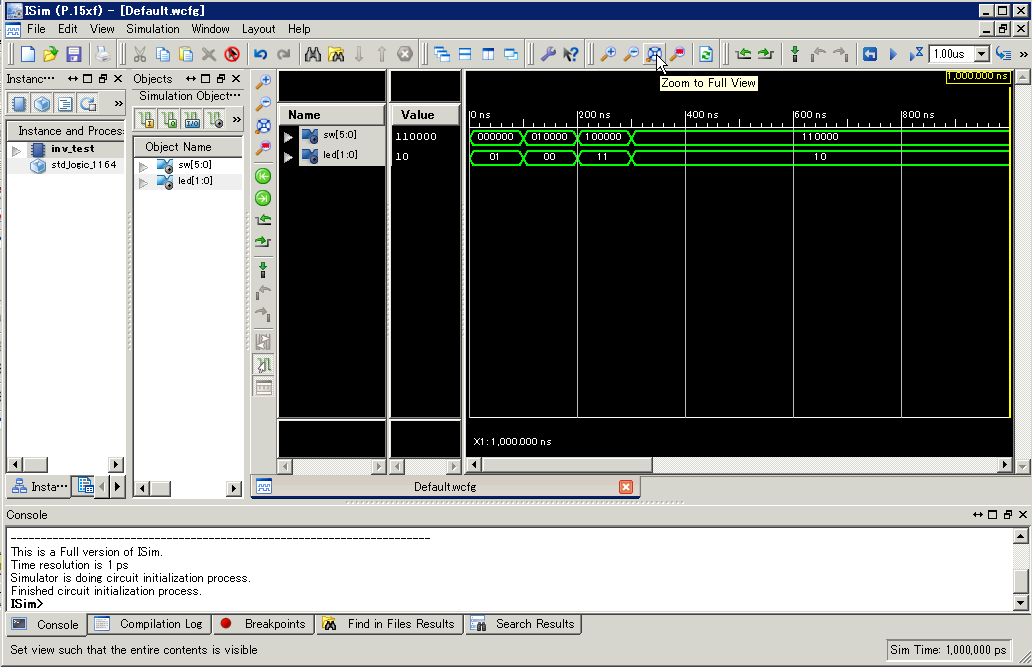

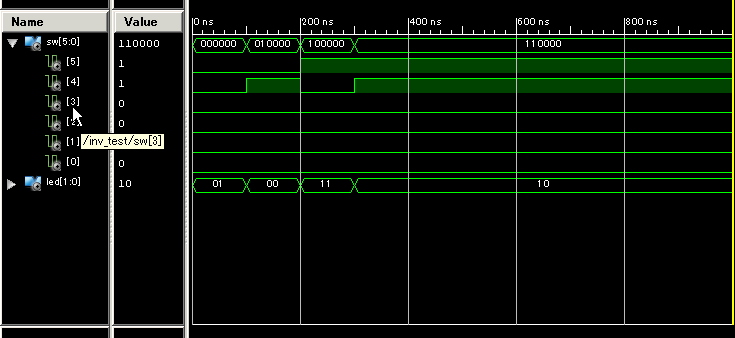

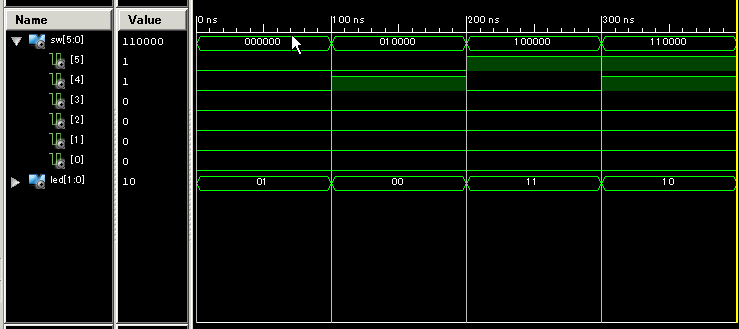

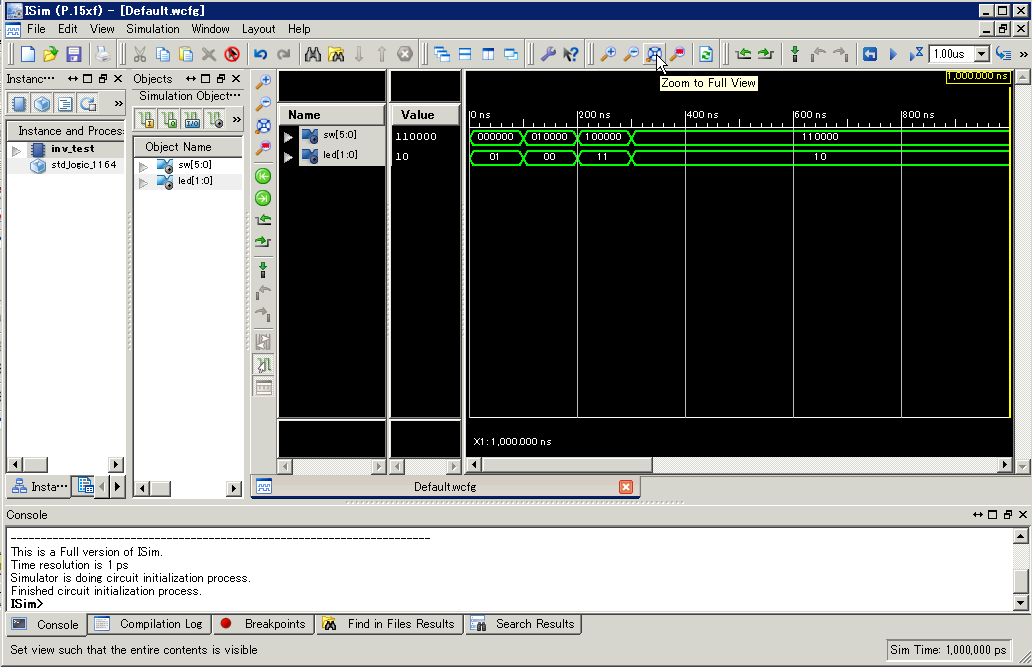

怴偟偄夋柺偑棫偪忋偑傝丄僔儈儏儗乕僔儑儞寢壥偑昞帵偝傟傑偡丅

偨偩偟丄嵟弶偼廔傢偭偨屻偁偨傝偺帪崗偺攇宍偑昞帵偝傟偰偄傑偡偺偱丄

僣乕儖僶乕撪Zoom to Full View傪墴偟偰

攇宍慡懱傪昞帵偟傑偡丅

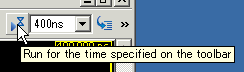

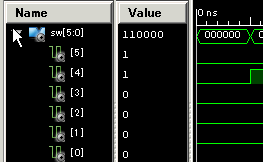

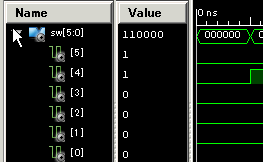

擖椡怣崋SW偼丄SW(0)乣SW(5)偺6杮偑傑偲傔偰昞帵偝傟偰偄傑偡偑丄

仾偺傛偆偵怣崋栚SW偺嵍偺仮儅乕僋傪僋儕僢僋偡傞偲丄

揥奐偟偰怣崋傪1杮偢偮妋擣偡傞偙偲偑偱偒傑偡丅

仺

仺

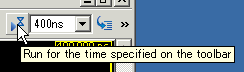

崱夞偺僥僗僩儀儞僠偱梌偊偨怣崋偱偼丄400ns傑偱偺僔儈儏儗乕僔儑儞偱

廫暘偱偟偨偺偱丄

僔儈儏儗乕僔儑儞偺幚峴傕丄偙偺400ns傑偱偵偟偰偍偒傑偟傚偆丅

仾恾偺傛偆偵丄夋柺塃忋偺曽偱廔椆帪娫傪400ns偵曄峏偟偨屻丄

Restart(僔儈儏儗乕僔儑儞傪儕僙僢僩)仺

Run for the time specified...

(巜掕帪崗傑偱僔儈儏儗乕僔儑儞傪幚峴)偺弴偱丄

僔儈儏儗乕僔儑儞傪幚峴偡傞偲丄寢壥偑昞帵偝傟傑偡丅

昞帵偝傟傟偰偄傞擖椡丒弌椡偺怣崋偑丄強朷偺幰偱偁傞偐傪妋擣偟偰偍偒傑偟傚偆丅

榑棟崌惉

僔儈儏儗乕僔儑儞偱丄愝寁偟偨夞楬偑惓偟偄偙偲偑妋擣偱偒偨傜丄

幚嵺偵FPGA儃乕僪(忋偺FPGA)偵彂偒崬傫偱摦嶌偝偣偰傒傑偟傚偆丅

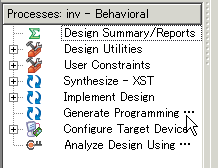

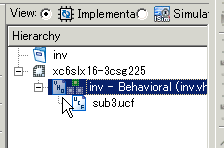

傑偢丄榑棟崌惉(僐儞僷僀儖)偡傞偨傔偵丄

嵍忋偺View:傪Implementation偵慖傫偱偍偒傑偡丅

懕偄偰丄乽愝掕僼傽僀儖乿傪嶌惉偟傑偡丅

偙偺乽愝掕僼傽僀儖乿偲偼丄巊偆擖弌椡(SW(4)偲偐LED(0)偲偐)偑丄

儃乕僪忋偺FPGA偺偳偺乽僺儞(抂巕)乿偵偮側偑偭偰偄傞偐丄傪

掕媊偡傞傕偺偱偡丅

偮傑傝FPGA偺奺擖弌椡抂巕偲僗僀僢僠傗LED偼丄偡偱偵儃乕僪忋偱

僴乕僪僂僄傾揑偵乽攝慄乿偝傟偰偄傑偡偺偱丄

VHDL偱婰弎偟偨夞楬傪摦嶌偝偣傞偨傔偵丄偙偺幚嵺偺攝慄偵偁傢偣傞丄

偲偄偆愝掕傪巜掕偡傞傢偗偱偡丅

崱夞偼偡偱偵偙偺儃乕僪梡偺乽愝掕僼傽僀儖乿傪梡堄偟偰偁傝傑偡偺偱丄

埲壓偺僟僂儞儘乕僪偟偰曐懚偟偰偍偄偰偔偩偝偄丅

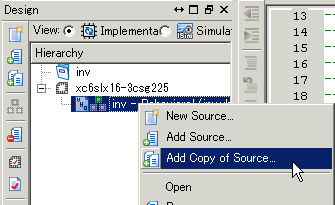

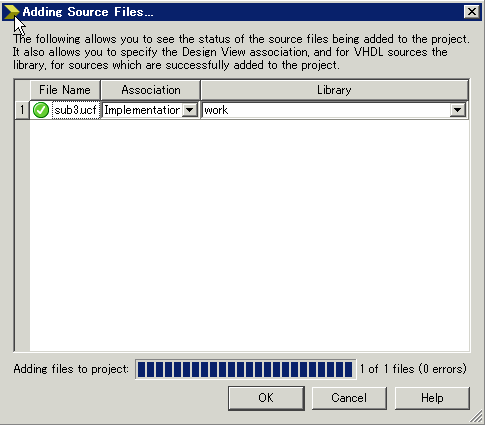

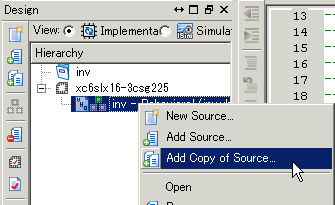

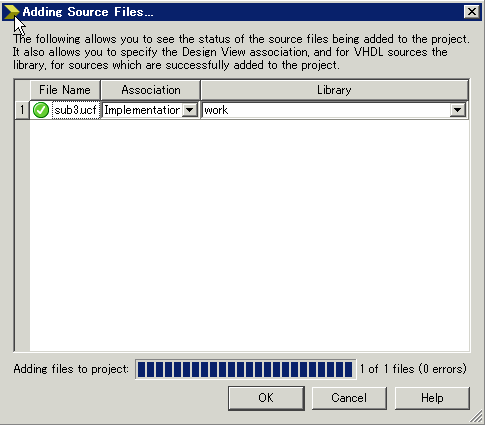

偙偺僼傽僀儖傪丄愝寁偟偰偄傞夞楬偵妱傝摉偰傑偡丅

夞楬偺VHDL僼傽僀儖偱偁傞inv傪

塃僋儕僢僋仺Add Copy of Source傪慖傃丄

偝偒傎偳僟僂儞儘乕僪偟偨sub3.ucf傪慖傫偱偍偒傑偡丅

偦偺sub3.ucf偑撉傒崬傑傟丄撪梕偑僠僃僢僋偝傟傑偡丅

(OK側傜椢偺僠僃僢僋儅乕僋偑偮偔)

仾偺傛偆偵丄夞楬杮懱偺inv.vhd偵丄愝掕僼傽僀儖sub3.ucf偑

妱傝摉偰傜傟偰偄傞偙偲偑妋擣偱偒偄傑偡丅

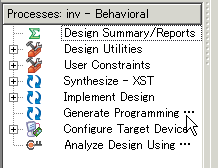

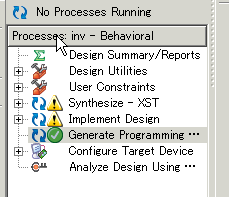

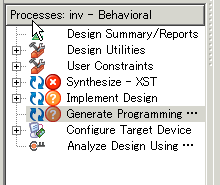

懕偄偰丄嵍壓偺Processes:撪偱丄

Generate Programming File傪僟僽儖僋儕僢僋偡傞偲

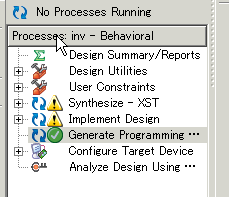

榑棟崌惉(僐儞僷僀儖)偑幚峴偝傟傑偡丅

彮偟帪娫偑偐偐傝傑偡偑丄仾偺傛偆偵椢偺僠僃僢僋儅乕僋偑偮偄偨傜

姰椆偱偡丅

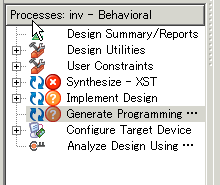

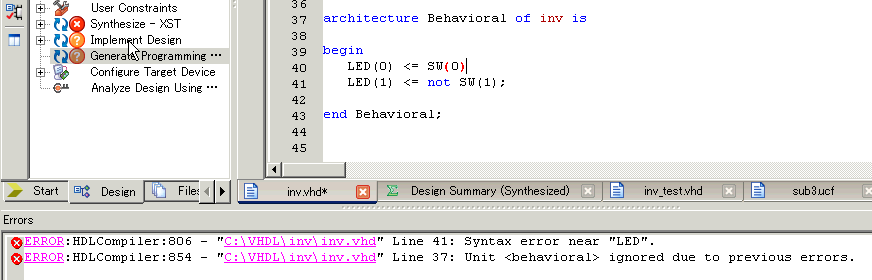

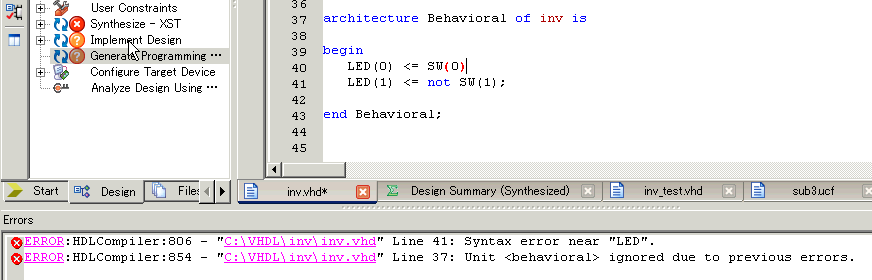

僄儔乕偑偁偭偨応崌側偳偱榑棟崌惉(僐儞僷僀儖)偵幐攕偟偨応崌偼丄

仾偺傛偆偵愒偺亊儅乕僋偑偮偔偺偱丄僄儔乕儊僢僙乕僕傪傒側偑傜

inv.vhd偺廋惓傪偟傑偡丅

僄儔乕儊僢僙乕僕偼塸岅偱偡偑丄梫揰偩偗撉傔偽傛偄偱偡丅

椺偊偽仾偺椺偱偼丄1偮傔偺僄儔乕偲偟偰

乽41峴栚偺"LED"偲偄偆扨岅偺嬤偔偵暥朄(Syntax)僄儔乕偑偁傞傛乿

偲側偭偰偄偰丄偨偟偐偵1偮慜偺40峴栚偺嵟屻偵僙儈僐儘儞(;)偑側偄偺偑

尨場偱偁傞偙偲偑傢偐傝傑偡丅

彂偒崬傒

偄傛偄傛榑棟崌惉(僐儞僷僀儖)偑廔傢偭偰姰惉偟偨夞楬傪丄

儃乕僪偵彂偒崬傫偱摦嶌偝偣偰傒傑偟傚偆丅

彂偒崬傒婡偼2庬椶偁傝傑偡偺偱丄奺帺偑巊偆傕偺偵偁傢偣偰愙懕傪偟偰偔偩偝偄丅

- Xilinx Platform Cable USB偲彂偄偰偁傞嵶挿偄崟偄敔偺応崌

仾偺傛偆偵愙懕偟傑偡丅僐僱僋僞偺岦偒偑媡偵側傜側偄傛偆偵拲堄丅

- DIGILENT偲彂偄偰偁傞彫偝偄崟偄敔偺応崌

仾偺傛偆偵愙懕偟傑偡丅僐僱僋僞偺岦偒偑媡偵側傜側偄傛偆偵拲堄丅

愙懕偑廔傢偭偨傜丄儃乕僪偲彂偒崬傒婡傪偦傟偧傟USB働乕僽儖偱PC偲愙懕偟傑偡丅

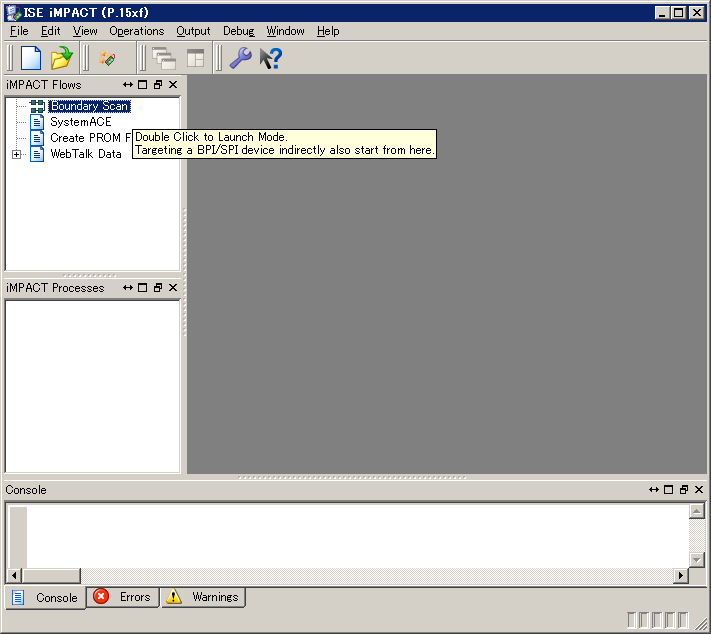

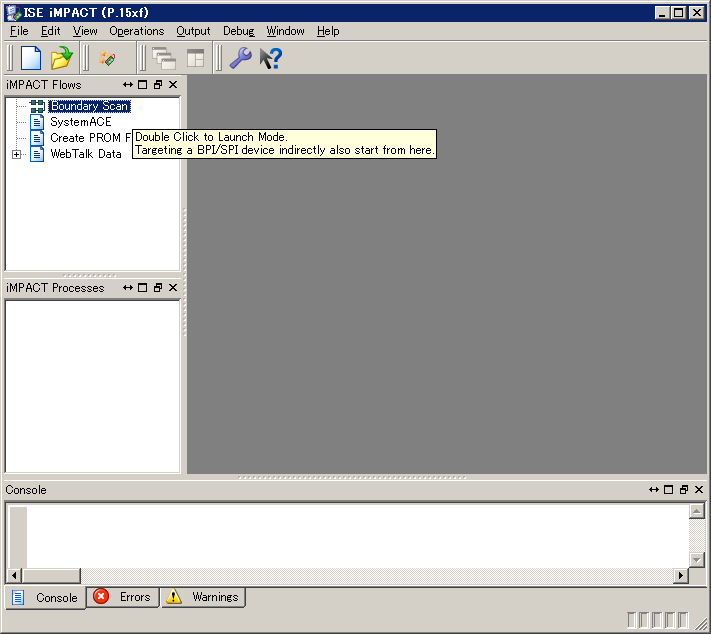

懕偄偰丄偝偒傎偳偺"Generate Programming File"偺偡偖壓偺

Configure Target Device傪僟僽儖僋儕僢僋偟傑偡丅

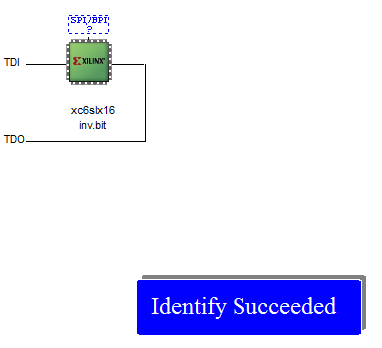

儃乕僪偺彂偒崬傒忣曬偑側偄傛(弶傔偰巊偆偺偱偁偨傝傑偊偱偡偑)偲

尵傢傟傞偺偱丄OK丅

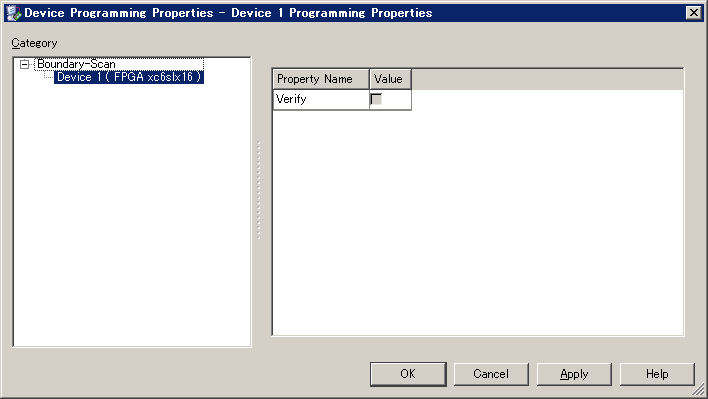

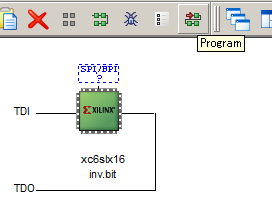

彂偒崬傒夋柺偵側傞偺偱丄嵍忋偺Boundary Scan傪

僟僽儖僋儕僢僋丅

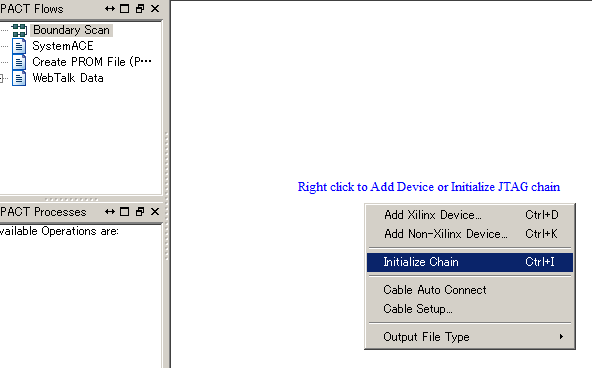

傑偭偝傜側夋柺偑偱傞偺偱丄

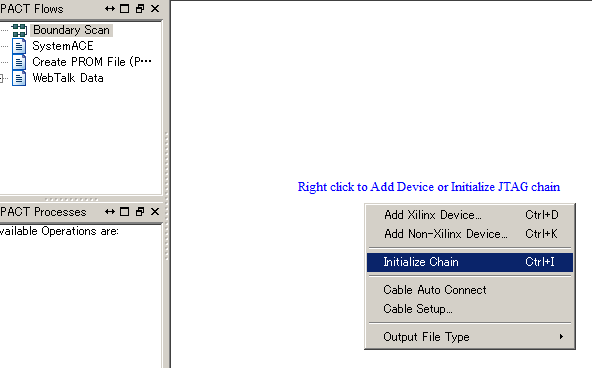

偦偙偱塃僋儕僢僋仺Initialize Chain傪慖戰丅

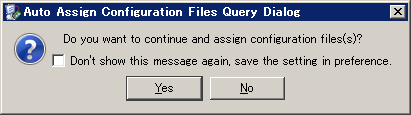

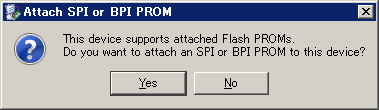

懕偄偰丄儃乕僪忋偺FPGA偵夞楬偺僼傽僀儖傪妱傝摉偰傑偡偐丠偲

暦偐傟傑偡偑丄偣偭偐偔嶌偭偨夞楬傪摦嶌偝偣傞偨偗偱偡偐傜丄傕偪傠傫Yes丅

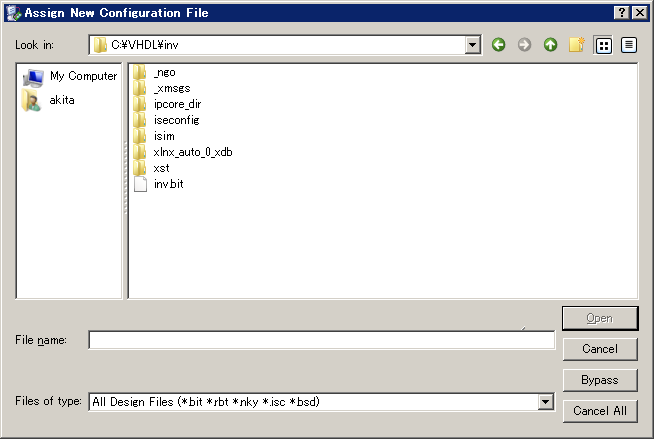

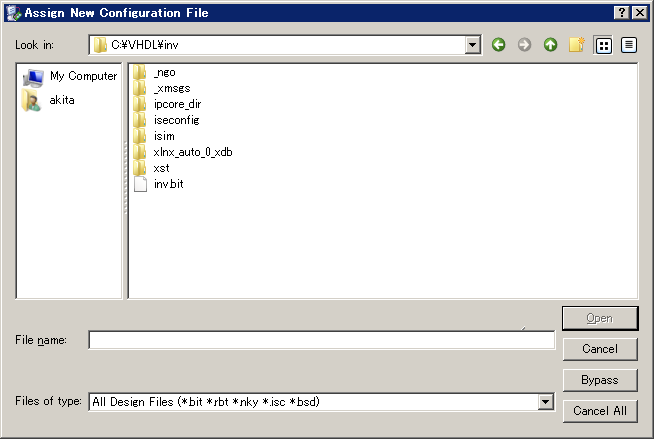

榑棟崌惉(僐儞僷僀儖)偺寢壥偺僼傽僀儖傪巜掕偡傞夋柺偵側傞偺偱丄

inv.bit傪慖傫偱偍偒傑偡丅(偙傟偑榑棟崌惉偑廔傢偭偨夞楬偺掕媊僼傽僀儖)

懕偄偰丄偙傫側夋柺偑弌傑偡偑丄偲傝偁偊偢No丅

(FPGA偵彂偒崬傫偩夞楬偼揹尮OFF偱徚偊偰偟傑偄傑偡偑丄偦傟傪儃乕僪忋偺

ROM偵曐懚偡傞偐偺慖戰偱偡偑丄偲傝偁偊偢偼巊偄傑偣傫)

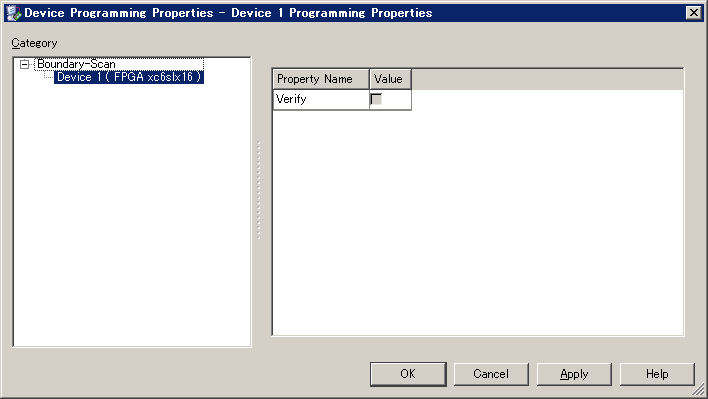

弨旛偑惍偭偨偙偲偺妋擣夋柺側偺偱丄OK丅

偙傟偱弨旛偑惍偄傑偟偨丅

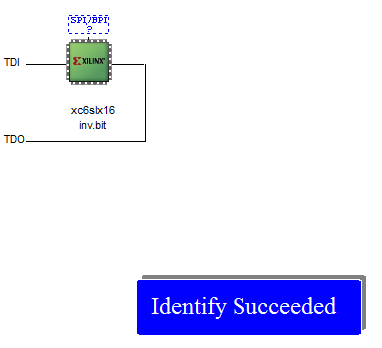

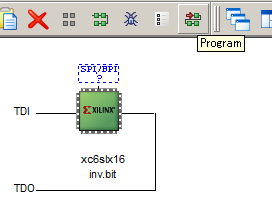

椢偺巐妏偺FPGA傾僀僐儞傪慖戰偟偨忬懺偱丄僣乕儖僶乕撪偺

Program傪墴偡偲丄嶌偭偨夞楬偑揮憲偝傟丄摦嶌傪偼偠傔傑偡丅

儃乕僪忋偺僗僀僢僠A, B傪墴偟偰丄LED A, B偑偳偺傛偆偵岝傞偐傪

妋擣偟偰傒傑偟傚偆丅

愝寁偟偨夞楬偳偍傝偺摦嶌偵側偭偰偄傞偼偢偱偡丅

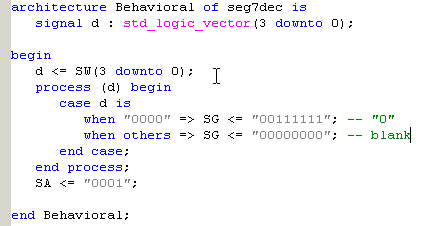

幚慔: 7僙僌儊儞僩LED

傕偆彮偟暋嶨側夞楬偲偟偰丄7僙僌儊儞僩僨僐乕僟傪偮偔偭偰傒傑偟傚偆丅

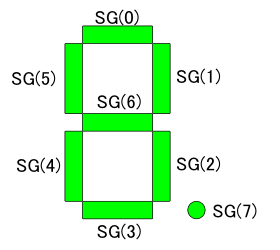

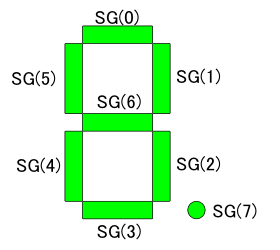

僒僽儃乕僪忋偺7僙僌儊儞僩偼丄8杮偺乽SG乿偲偄偆弌椡怣崋偵偮側偑偭偰偄偰丄

偦傟偧傟伀偺傛偆偵偮側偑偭偰偄傑偡丅

椺偊偽SG(1)偲SG(2)傪"1"丄偦傟埲奜偵"0"傪弌椡偡傞偲丄

乽1乿偲偄偆悢帤傪昞帵偱偒傞偙偲偵側傝傑偡丅

偟偨偑偭偰丄乽0乿乣乽9乿(偁傞偄偼16恑悢傕娷傔偰

10乣15偵懳墳偡傞乽A乿乣乽F乿傕)偺悢帤丒暥帤傪昞帵偱偒傞傛偆偵丄

昞帵偟偨偄抣(0乣9/15側偺偱4價僢僩)傪梌偊傞擖椡d偺偦傟偧傟偵懳偟偰丄

弌椡偡傞傋偒SG(0)乣SG(7)偺抣偺懳墳傪偁傜偐偠傔媮傔偰

恀棟抣昞傪偮偔偭偰偍偗偽丄偦傟傪VHDL偱婰弎偡傟偽傛偄偙偲偵側傝傑偡丅

(傑偝偵慜夞傒偰偒偨僨僐乕僟偺婰弎偑棳梡偱偒傑偡)

婎杮揑偵偼偝偒傎偳偺NOT僎乕僩偲摨條偺庤弴偱

怴偟偔夞楬傪偮偔傝傑偡丅

(帪娫偑懌傝側偄偐傕偟傟傑偣傫偑丄

偤傂僔儈儏儗乕僔儑儞丄幚嵺偺摦嶌傑偱偟偰傒傑偟傚偆)

堘偆揰偺億僀儞僩偩偗偁偘偰偍偒傑偡丅

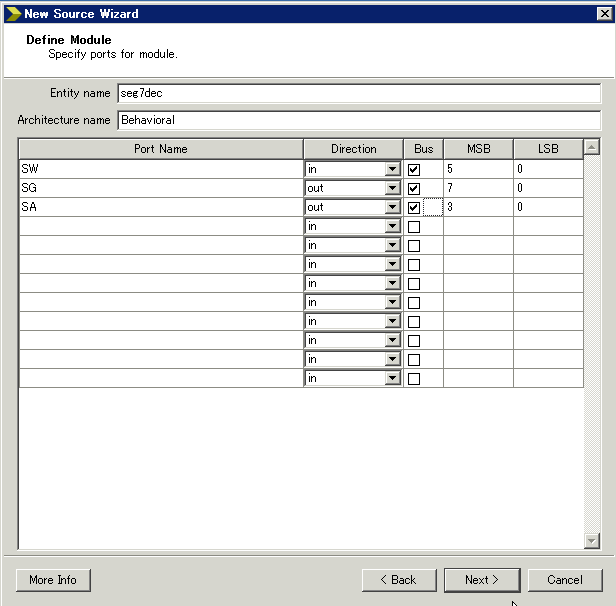

- 夞楬偺擖弌椡偺掕媊偱偼丄乽SW乿6杮丄乽SG乿8杮丄乽SA乿4杮丄傪

巜掕偟偰偍偒傑偡丅

6杮偺SW偺偆偪丄SW(0)乣SW(3)偼丄埲壓偺傛偆偵廫帤攝抲儃僞儞偵懳墳偟傑偡丅

- SW(0) : 忋(仾)

- SW(1) : 塃(仺)

- SW(2) : 壓(伀)

- SW(3) : 嵍(仼)

- SW(0)乣SW(3)傪4價僢僩偺抣傪梌偊傞擖椡偲偟偰巊偆偙偲偵偟傑偡丅

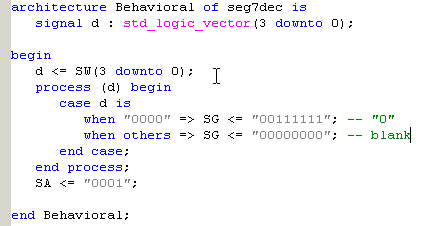

偦偙偱埲壓偺傛偆偵signal偲偟偰4價僢僩偺d傪掕媊偟偰偍偒丄

傑偢偼偦偺d偵SW(3乣0)傪偮側偄偱偍偒傑偡丅

偦偟偰7僙僌儊儞僩僨僐乕僟偺婰弎偼丄慜夞偺僨僐乕僟偺婰弎傪嶲峫偵丄

偙偺d偵懳偡傞応崌暘偗傪暲傋偰彂偄偰偍偒傑偡丅

(埲壓偺婰弎偱偼"0000"仺乽0乿偟偐彂偄偰偄側偄偺偱丄

偙傟傪乽9乿傑偱丄傑偨偼16恑悢懳墳偱乽A乿乣乽F乿傑偱婰弎偡傞)

側偍弌椡偺SA偼丄仾偺傛偆偵"0001"傪梌偊偰偍偄偰偔偩偝偄丅

(偙傟偵傛偭偰塃抂偺7僙僌儊儞僩LED偺傒揰摂偟傑偡)

- 愝掕僼傽僀儖偼丄7僙僌儊儞僩LED梡偺僺儞攝抲傕娷傔偨愝掕僼傽僀儖傪巊偄傑偡丅

栠傞

仺

仺