番号

氏名

一部 图 新

1. 次のような論理回路の VHDL 記述で、それぞれの process 文のセンシティビティ・リスト(sensitivity list)に記述するべき信号名を過不足なく記せ。(10点×4)

```

entity hoge is

port (

a, b, c : in std logic;

w, x, y, z : out std logic

end hoge;

(左下から続く)

process ([3]) begin

architecture arch of hoge is

case a is

begin

when '1'

=> y <= x;

process ([1]) begin

when '0'

=> y <= z;

case a is

end case;

when '1'

=> w <= a;

end process;

when '0' \Rightarrow w <= b and c;

end case;

process ([4]) begin

end process;

case a is

when '1'

=> z <= b;

process ([2]) begin

when '0' => z <= not b;

case b is

end case;

when '1'

=> x <= '1';

end process;

when '0' => x <= '0';

end arch;

end case;

end process;

(右上へ続く)

```

[1]: a, b, c

[2]:

[3]: a, 2,2

学部はない

[4]: a, b

2. 次のような VHDL 記述された論理回路の論理プロック (インスタンス:四角で囲って図示) の名称や論理ゲートの接続関係を、例にならって必要であれば論理ゲートと各信号線の名称とともに図示せよ。(10点)

```

例:

entity hogel is

port (a, b: in std logic;

x: out std logic);

end hogel;

architecture arch of hogel is

component hoge2

port (a: in std logic,

b: out std logic);

end component;

signal w0, w1: std logic

begin

i0: hoge2 port map(a=>a, b=>w0);

i1: hoge2 port map(a=>b, b=>w1);

x \le w0 and w1;

end arch;

hogel

iO(hoge2)

w0

- X

i1(hoge2)

b

a

b

w1

```

```

entity hoge3 is

port (a, b, c: in std logic;

y: out std_logic)); x zzt127-16-11

end hoge3;

※生力工、当まかりは

architecture arch of hoge3 is

見はなって

component abc

port (a, b: in std_logic, x: out std_logic);

end component;

component def

port (a, b: in std logic, x: out std logic);

end component;

signal w0, w1: std logic;

begin

i0: abc port map(b=>a, a=>b, x=>w0);

il: abc port map(a=>a, b=>c, x=>w1);

i2: def port map(x=>y, a=>w0, b=>w1);

hoge3

x \le not y;

end arch;

(olabe)

C

22(def)

wo

9

21(262)

9

```

BLIE 36-6 - 12-9

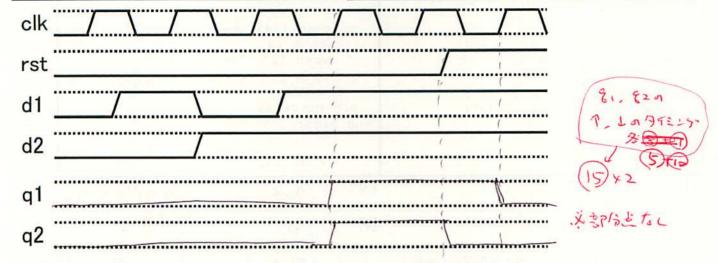

3. 次のような 2 種類の回路 hoge1, hoge2 に以下の図のような信号を与えたときの出力 q1, q2 を図示せよ。ただし q1, q2 の初期値は'0'とする。また g1, q2 の変化のタイミングを、対応する信号のタイミングと結ぶ縦の点線で明示すること。 (15点×2)

```

entity hogel is

port (clk, rst, dl, d2: in std_logic;

q1: out std_logic));

end hogel;

architecture arch of hogel is

begin

process (clk, rst) begin

if (clk'event and clk = '1') then

if (rst = '1') then ql <= '0';

else ql <= dl and d2;

end if;

end if;

end process;

end arch;</pre>

```

4. 講義で扱った進カウンタの VHDL 記述を参考に、出力値が 0~27 の範囲で順番に増える 28 進カウンタ count 28 の VHDL 記述を完成させよ。ただし信号のビット数は必要十分な数とし、リセット動作は同期リセットとする。(20点)

```

entity count28 is

port (clk, rst, dif: in std logic;

q: out std_logic_vector( & (_downto 0));

end count28;

architecture arch of count28 is

signal q_reg : std_logic_vector( \ downto 0);

process (clk) begin

if (clk'event and clk = '1') then

if (rst = '1') then q_reg <= " 00000

if (q-reg = 27) then q-reg (= "00000")

else q-veg (= g-reg +1)

もらんかでしけれるり~~

ヒントもちから

文はもちかつ 一人

end if;

end if;

屋かららいろ 一点

end process;

q <= q req;

end arch;

```