- 履歴一覧

- 差分 を表示

- 現在との差分 を表示

- ソース を表示

- yamamura へ行く。

- 1 (2014-04-17 (木) 13:58:30)

- 2 (2014-04-17 (木) 14:26:03)

- 3 (2014-05-15 (木) 15:24:33)

- 4 (2014-05-16 (金) 09:54:45)

- 5 (2014-05-22 (木) 16:14:37)

- 6 (2014-06-19 (木) 16:58:07)

- 7 (2014-06-24 (火) 15:42:45)

- 8 (2014-06-24 (火) 22:01:24)

- 9 (2014-06-26 (木) 16:58:55)

- 10 (2014-07-15 (火) 14:05:37)

- 11 (2014-08-18 (月) 10:01:20)

- 12 (2014-10-26 (日) 12:04:00)

- 13 (2015-04-21 (火) 18:08:10)

- 14 (2015-04-23 (木) 02:40:36)

- 15 (2015-06-08 (月) 17:52:05)

- 16 (2015-07-17 (金) 23:15:13)

- 17 (2015-09-02 (水) 18:16:25)

- 18 (2015-09-09 (水) 17:39:23)

- 19 (2015-09-14 (月) 14:29:37)

- 20 (2015-09-17 (木) 13:45:00)

- 21 (2015-10-22 (木) 11:29:56)

- 22 (2016-03-15 (火) 18:16:37)

- 23 (2016-03-18 (金) 12:11:58)

- 24 (2016-03-19 (土) 10:45:53)

- 25 (2016-05-09 (月) 17:54:56)

- 26 (2016-05-11 (水) 14:25:35)

- 27 (2016-05-11 (水) 14:25:35)

- 28 (2016-06-21 (火) 14:26:21)

- 29 (2016-07-05 (火) 10:33:33)

- 30 (2016-07-07 (木) 10:15:07)

- 31 (2016-10-14 (金) 16:28:28)

- 32 (2016-12-02 (金) 14:43:26)

- 33 (2017-01-16 (月) 15:50:01)

- 34 (2017-01-16 (月) 19:07:37)

- 35 (2017-01-16 (月) 19:07:37)

- 36 (2017-01-17 (火) 17:51:35)

- 37 (2017-01-17 (火) 17:51:35)

- 38 (2017-01-17 (火) 17:51:35)

- 39 (2017-01-17 (火) 17:51:35)

- 40 (2017-01-30 (月) 20:04:17)

- 41 (2017-02-06 (月) 10:17:57)

目次

挨拶†

新しくifDLに配属されたB4の山村聡史です。 これからよろしくお願いします。

作業日誌†

2017†

1/16(月) TeXで修論を書いてて調べた事とか†

- 複数行のコメントアウト

- commentパッケージを使えば\begin{comment} ... \end{comment}で複数行コメントアウトできる

- %を使えば次の改行までコメントアウト

- 画像を並べて貼る

- subfigure環境を使う

- tabularと組み合わせて使えば,マトリクス状に配置可能

- 要素を & で並べて,\\で改行

- 複数行の計算式をイコールで揃えていい感じにする

- eqnarray環境を使う

- 揃えたい基準アルファベットの前後に"&"を加えると揃う

- 改行は\\でする

- 改行せずに&=&とかを書くとエラー

- 途中式に番号つけたくない場合は\nonumber

- 天井関数の書き方

- 数式環境の中で\left \lceil .... \rifgt \rceil

- 床関数とかその他かっこっぽい記号は大体似たような記述

- 章末に画像を乗っけると,ページの上部ではなくど真ん中に配置される

- 普段は\begin{figure}[h]にすれば,文中にいい感じで配置される

- 章末等うまくいかない時は[h]を[H]にすれば大体うまくいく

- キャプションの途中で改行をする

- 結論から言うと,あまり綺麗にそろえる手段は分からなかった

- \protect \newlineで改行すると,中央揃えが崩れて左揃えになる.微妙

- \protect \linebreakだと,文字がページ幅に均等配置される.気持ち悪い.

- $...$の数式オプションを使えば何とか掛けるが,図見出しが気持ち悪くなる

- caption環境を使うと強引に改行できるらしいが未検証

- あきらめて改行しなくてもいい長さのキャプションで我慢する

2016†

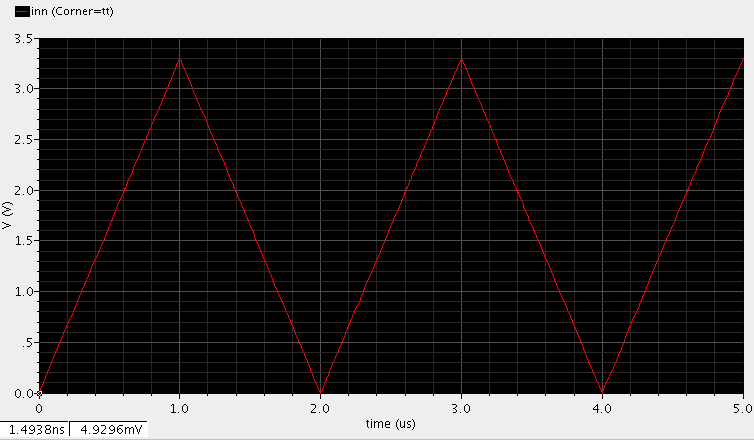

3/15(火) virtuoso ADEで三角波を入力する†

回路図の入力電圧源としてanalogLibのvpwlというインスタンスを使うと簡単に生成できる。

各パラメータの意味は以下の通り。

- Number of pairs of points

- 波形の特徴点の数(特徴点以外は線形に補間されるっぽい)。のこぎり波なら2、三角波なら3等、波の形を自由に定義できる。

- Time 1、Voltage 1

- 特徴点1の時間と電圧値を設定。

- Time 2、Voltage 2

- 特徴点2の時間と電圧を設定。以下Number of pairs of pointsの値によってTime 3、Time 4・・・と追加表示されていく。

- Period of PWL

- 波形の周期。この値秒ごとにTime 1、Voltage 1・・・で設定した波形が繰り返される。

例として周期2usecの三角波を挙げると、以下のパラメータでこんな感じの波形ができる。

- Number of pairs of points=3

- Time 1=0 ,Voltage 1=0

- Time 2=1u ,Voltage 2=3.3

- Time 3=2u ,Voltage 3=0

- Period of PWL=2u

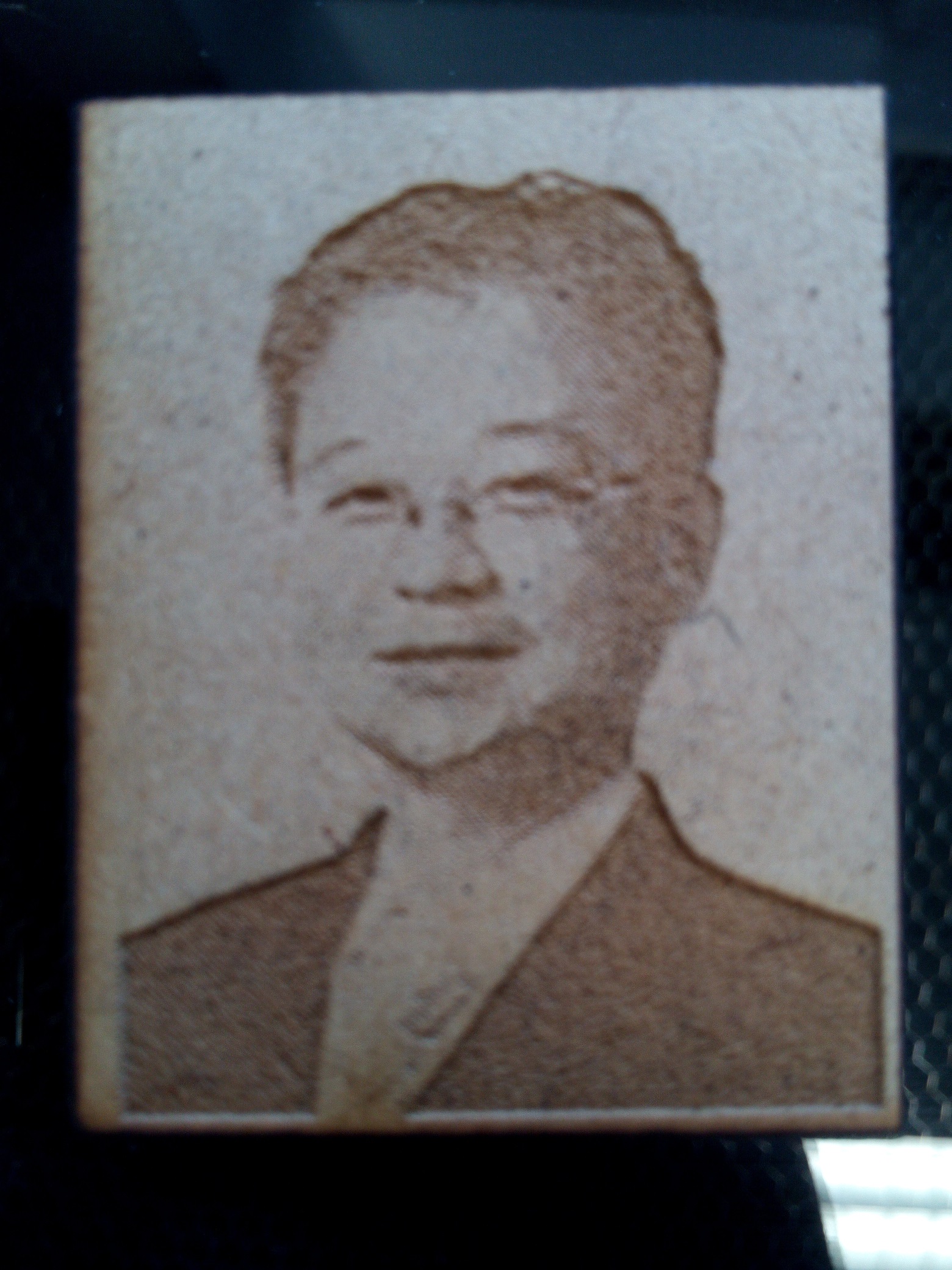

3/17(木) レーザーカッターで写真等を刻印する†

まったり部屋のレーザーカッターを使うと、8bitのグレースケール画像を刻印できる。

画像編集ソフトで8bitグレースケールに変換してpng等で保存し、あとは普通のカッティングと同様の手順でOK。

刻印する画像は、コントラストを調整しないと、濃淡がうまく表現できない場合が多い。ヒストグラムを使ってコントラストを調整できるソフトを使うと細かい調整ができる。

参考として、人物画像は肌が真っ白になるくらいが丁度良い感じだった。また、材質によっても出来は変わるので、何度か練習印刷した方が良い。

- 例:北川先生の写真をMDFに刻印

5/9(月) virtuosoのライセンス更新に関しての記録†

金沢大学のCADサーバーは、東大VDECからライセンスを参照しているが、今年の5/1にライセンスの更新があり、金沢大学のライセンスはまだ更新できていないようなので、名古屋大学のサーバのライセンスを一時的に利用させてもらうことになった。

ライセンスの参照先は ~/setlic からたどっていけば分かるが、/user 以下を勝手に変更するのはまずいと思ったので、以下の手順で変更した。

(以下の手順は集積回路工学等で北川先生が用意してくださった設計環境を元に記載してあるので、setlicのありかや中身は違う場合があるかもしれません。参考程度に。)

- cp /user/cadence/cshrc.ic613_MMSIM ~/cshrc.ic613_MMSIM

~/cshrc.ic613_MMSIM の中の setenv CDS_LIC_FILE 5280@vdec-cad1: ・・・ を#でコメントアウト

- 下に setenv CDS_LIC_FILE 5280@○○○.○○○.○○○.○○○ (参照先コンピュータのIPアドレス)を追加して保存

~/setlic の source /user/cadence/cshrc.ic613_MMSIM を#でコメントアウト

- 下に source ~/cshrc.ic613_MMSIM を追加して保存

これでライセンスの参照先が一時的に変更できる。

戻すときはsetlicを書き直せばおk。

追記:東大のライセンスが使えるようになったので、setlicを元に戻しても使えるようになりました。

6/21(火) 回路をアレイ状に並べるときの電源の引き方†

イメージセンサなどアレイ状に回路を並べて並列に読み出し等を行う場合、回路が同時にアクティブになる方向に電源ラインを引くと、1つの電源ラインに電流が集中するため、中心に向かって電源電圧が降下しやすい。

メッシュ状に電源を引き回すのがもちろん最良だが、スペース的に厳しい場合はどの方向に電源ラインを引くか考えてレイアウトすると良い。

7/4(月)virtuoso, calibreのいくつか備忘録†

- Layout XLのスケマと対応を取って配線の支援をしてくれる機能は、呼び出すインスタンスにCreate Pinで作ったピンオブジェクトがないと機能しない。

- ただし、Calibre LVSではピンオブジェクトではなく、LSW画面のPurposeがpinのレイヤーでピン名に対応したラベルを配線上におかないと対応が取れない。

追記:スケマからインスタンスを自動生成する際にピンも生成できるのだが、その時にピンのラベルも自動で生成できる。その際にラベルレイヤーをLVSに対応したレイヤーに設定すれば、ピンオブジェクトとラベルをいっぺんに生成できる。

- ただし、Calibre LVSではピンオブジェクトではなく、LSW画面のPurposeがpinのレイヤーでピン名に対応したラベルを配線上におかないと対応が取れない。

- スタセルなど、中のレイアウトは見れず配線のみのデータが提供されているセルをインスタンスとして呼び出している回路のLVSをするときは、Calibre LVSのルールファイルの中に "LVS BOX CELLNAME"という記述が必要。

- たとえば "AND2"というスタセルを含む回路のLVSをする場合は、"LVS BOX AND2" とルールファイルに記述する。

- また、LVSのオプションで普段はFlatにしているところをHierarchicalにする。

- ADEを使った回路シミュレーションで、多少込み入った制御信号が必要な場合、電圧源としてanalogLibのvbitを使うとよい。vpulseでは単純な繰り返しパルスしか記述できないが、vbitならばパルスのタイミングや幅をかなり自由に定義可能。必要に応じてvpulseとvbitを使い分けよう。

- vbitの各種パラメータ

- pattern Parameter data :パルスに対応したビット列。'0'か'1'のみ。 例)010110など

- Pattern Parameter rptstart :繰り返すとき、ビット列のどの位置から始めるか。1以上ビット列長以下の整数のみ

- Pattern Parameter rpttimes :繰り返し回数。1以上の時、rptstartビット目からビット列を繰り返す。

- One value :ビット列の'1'に対応する電圧

- Zero value :ビット列の'0'に対応する電圧

- Delay Time :信号生成をどの時間から始めるか

- Rise time :信号の立ち上がり時間。

- Fall time :信号の立下り時間

- Period :何秒間で1ビットを出力するか

Rise timeやFall timeを短くしすぎると、シミュレーションの単位時間の問題か、出力がバグる。Periodの1/10から1/100位が妥当か。

- vbitの各種パラメータ

10/14(金) XILINX ISEを使ったFPGAの設計に関していくつか調べたこと†

- FPGAのIOピンとHDL中のネット名の対応はucfファイルに記述すればよいのだが、設計途中でucfには記述したが、実際のHDLでは未使用のネットが存在するとインプリメントの時に"constraintSystem:59"というエラーが出てしまう。

これを回避(というか一旦無視)するには、Implement designのプロパティでtranslate propertiesのAllow Unmatched LOC constraintsにチェックを入れれば、未使用のネット定義を自動で除去してくれる。ただし、無視しましたという旨のワーニングがいっぱい出る。 - ucfでLOCをしていない、完全に未使用のIOピンは、ISEの設定によっては自動でプルアップされることがある。

未使用ピンの処理やピン制約のミスなどによっては、回路を破壊したりする恐れがあるので、Generate programming Fileのプロパティから、Configuration Options-Unused IOBをフロートにしておいた方が無難らしい。

12/02(金) 修論のpLaTeXテンプレ†

修論用のtexソースとして卒業した先輩方の物を利用しようとしたときに,エンコードがバラバラで文字化けやコンパイルが出来ないところがあったので,すべてUTF-8に統一して,merl_ifdl_share/Template_MasterThesisにおいたので,これから修論を書く方は参考にしてください.

2015†

4/21(火) 変数の型について(超基本)†

ArduinoとマトリクスLEDで日付表示板を製作。

年月日時刻のうち年だけうまく表示されない・・・

設定した年と表示される年が一致せず、ダウンロードしてきたライブラリの中身を見たりいろいろ試した結果、年を代入する変数にbyte型を使っていたことが原因だと気が付く。

byte型は8bitなので、0〜255までしか代入できないのに、2015という数字を代入したため、オーバーフローしておかしな数字になっていた。

他の月日や時間はbyte型で収まる範囲だったため、そのままよく考えずにbyte型で宣言してしまった。

久しぶりのプログラミングで、超基本事項でつまづく失態を犯してしまった・・。

Cで型の宣言をするときは、代入する数値の範囲をよく考えよう(戒め)。

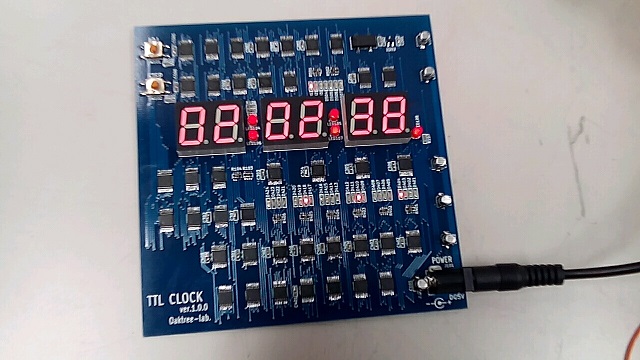

4/22(水) ハードウェアのデバッグ†

秋田先生からもらったTTL時計キット(oaktree_labさん販売)を組み立てた。

3時間くらいではんだ付けは終了したが、いつも通り一発では動かない。

オシロスコープを使って水晶発振器部分から回路図をたどり、挙動と合わせて考えて、怪しいところを片っ端から確認作業した。

結果3か所くらい接触不良やはんだのブリッジを見つける。

最終的にはうまく動作させることができた。

久しぶりにがっつりとはんだ付けをして、いい練習になった。

また、TTL回路ですらデバッグ作業にそこそこ時間がかかったことを考えると、ハードウェアのデバッグは本当に大変だと思った。

こんな感じの表面実装ロジックゲートがいっぱい

6/8(月) MOSFETのW/Lについて†

ミクストシグナルの課題をやっていて,L : 1um, W : 1um Multiply : 25 でカレントミラー回路のシミュレーションを行ったところ,飽和領域のIds-Vds特性が非常に悪くなり,北川先生に質問した.

検証の結果,どうやらLに対してWが十分に大きくないと,Narrow Gate効果という物が働き,MOSの特性が著しく悪化していたようだ.

Multiplyで実効的なゲート幅を稼いでいるから問題ないだろうと考えていたが,物理的な構造がMOSの特性に大きく影響しているという事実を実感した.

Wを10um以上にすればおおよそ理想的な特性が得られたため,アナログ回路ではW/LをMultiplyやFingar 無しで10程度は確保しておいたほうが良さそうである.

7/17(金) アルミを使った回路について†

アルミはハンダ付けが出来ないので,アルミ箔やアルミテープを使った回路はやめよう(戒め).

9/2(水) 初ワイヤボンディング†

7月まで設計していたチップが先日届いたので、測定のため、初ワイヤボンディングをした。

ボンディングマシンの原理自体はそんなに複雑なものではないが、アルミワイヤがとにかく細いので(20um)、セッティングが非常に大変。

ボンディング中にワイヤが抜けたり曲がったりするとまたやり直しなのでお腹が痛くなる作業だった。

秋田先生に、ワイヤを先端の穴に通す方法や、必要な道具(先生の2015/09/02作業日誌参照)など、いろいろとノウハウを教えていただいたので、今度時間があるときに練習しておこうと思う。

特に先端の穴にワイヤを通す作業は、心眼が必要になるのでかなりの練習が必要。

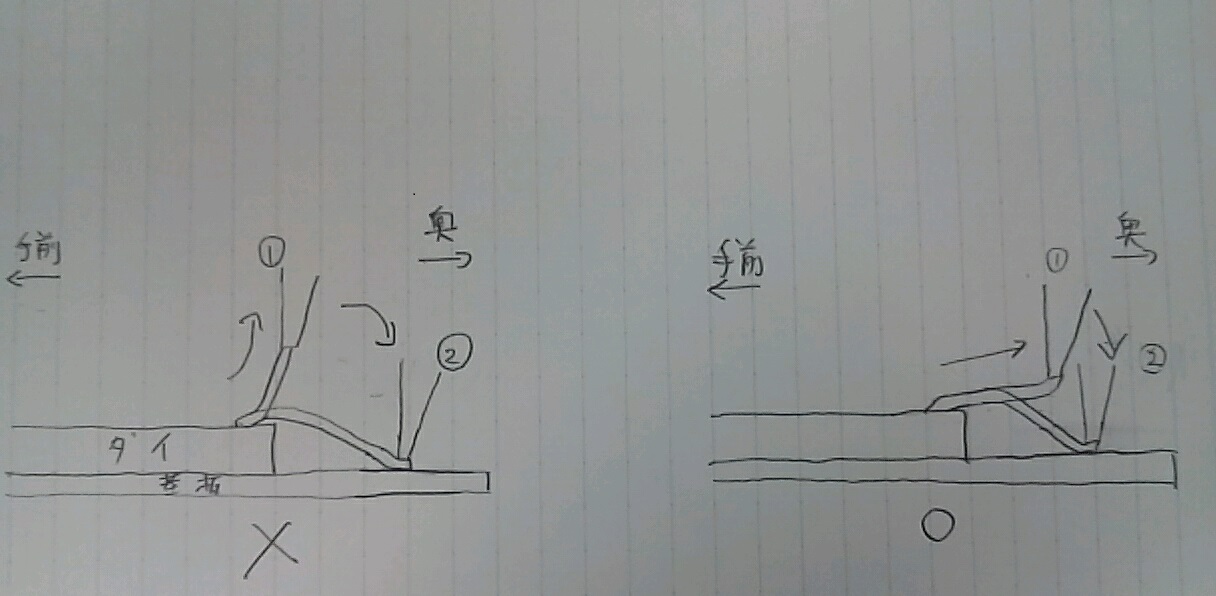

9/9(水) ワイヤボンディングのコツとか†

- ボンディングは手前から奥方向に行う

- パッドと基板が顕微鏡で見たときにy軸上にあるように基板の位置、角度をあらかじめ調整しておく

- 1stボンド後、ワイヤにテンションを掛けすぎるとワイヤが外れてしまう

- 特に一度失敗したパッドは、アルミのカスが残って、くっつきにくくなる。

- 今まで、テンションを掛けないために、1stボンド後に上に持ち上げてワイヤをたるませていた

- 何度が失敗するうちに、持ち上げると基板に向かって降ろしていった際に、ワイヤが逆流していることが判明

- ワイヤの逆流によって、2ndボンド後に、ワイヤが切れなかったり、次のワイヤが出てこない(ウェッジ手前で折れ曲がってしまう)、最悪の場合ウェッジ内でワイヤが弛み、詰まりを起こすことが分かった

- 厚めのチップをボンディングするときは、1stボンド後に奥方向にワイヤを延ばしながら基板のランドに触れることで、ワイヤが逆流せず、スムーズに次のボンディングができる

9/15(火) イメージセンサに入る光量を減らす†

イメージセンサで撮影を行うとき、周囲が明るすぎると画素の電荷が飽和してしまってうまく撮影できなくなる。

これをシャッタースピードで調整することもできるが、フィルタによって減光するという方法もある。

ND Filter (Neutral Density) は主に可視光領域付近の光をほぼ均一に吸収するフィルタで、発色等を変えずに光量を減らすことができる。減衰量はND○○の場合○○分の1。

NDフィルタを使って非常に長いシャッタースピードで定点撮影することで、人などの動くものを消し去ったような写真を撮ったりもできるらしい。

9/17(木) Inkscapeで、オブジェクトサイズの指定ができなくなるバグ†

Windows版Inkscapeで、オブジェクトサイズを直接指定する欄に数値を入力できなくなることがある。

OSが64bitならば、64bit用Inkscapeを入れれば大丈夫らしい。OSが32bitの場合、古いバージョンのInkscapeならば、このバグがないらしい。

10/22(木) verilogで未定義の変数を使ってしまうミスを防ぐ記述†

verilogで未定義の変数を使うと1bitのwireと自動で解釈されてしまい,エラーにならない(Warningにはなる事が多い).

そこでコードの頭に

`default_nettype none

と記述すると,未定義の変数を使った時にエラーが出るので便利.

2014†

4/17(木) 作業日記初日†

今日は矢敷先輩、笹田先輩にプリンターの設定、ifDLwikiやBBSの使い方、半田部屋などの使い方などを教えてもらったので早速更新してみた。

5/15(木) I2Cについて†

最近取り組んでいた、I2C通信を用いたLCDの制御がようやくできたので、信号の確認とオシロスコープの使い方の勉強のために、昨日BBSに載っていた(ディジタル)オシロスコープ測定入門を参考にしながら、I2Cの波形を測定した。 I2Cのプロトコル通りの波形が測定できて少し感動した。

5/22(木) マイコンペについて†

作るもの:グループ分けデバイス

詳しく:マスタといくつかのスレーブが通信して、グループ分けとその表現をする

表現方法:液晶とか色とか音とか?

通信方法:有線?無線?通信方式は?

気になるワード:PICマイコン、UART、Xbee、フルカラーLED、赤外線通信、MIDI など

6/19(木) マイコンペの作品†

マイコンペに出す作品がだいたい完成した。

あとは来週届くプリント基板にハンダ付けするだけ(のはず)。

作品制作を通してつまづいた所や分かったこと、教えてもらったことなど

- PSoCの割り込みについて

割り込みを使うときはアセンブラで直接書くか、#pragma interrapt_handler を使ってCで書く。

割り込みをする時は、各種レジスタの設定が必要(PSoC Designerではm8c.hに色々定義されてます)

割り込み関数名を任意にする場合は、boot.asmの中の呼び出し関数名を書き換えればよいが、PSoC Designerでは、ビルドをするとboot.asmの内容が自動で更新されるので、そのたびに書き換える必要がある。

割り込み中に割り込みが発生すると割り込みルーチンから抜けた途端次の割り込みにルーチンに入ってしまうので、

- 割り込みルーチン中の処理はできるだけ簡単にする(フラグを立てるだけなど)

- 長い処理の場合、割り込み禁止にしておく

- UARTなんかは結構時間を食うので割り込み中ではしないほうが吉

- GPIOなどの外部割り込みの場合チャタリングなどを考慮する

- EAGLEについて

楽しい(ライブラリの作成は大変らしい)

配線や部品は基本的にgridで設定したピッチに従うが、Altを押しながらならグリッドの半分のピッチでおける。細かい配線では結構役に立つ。

部品の位置を微調整するときは右クリックからpropertyを使えばよい。

表面実装のパーツは、ヘッダコネクタなどを使って基板から浮かせる部品と重ねて置くこともできる。

パーツの配置は配線の難しさにかなり影響するようで、パーツ配置を色々試行錯誤すると案外スッキリ配線できたりする。 - XCTU(OSX ver)について

XBeeシリーズ1をXCTUで設定している時に気がついたこと

- ブロードキャストしようとDestination Addressを0xFFFFにしようとすると、何故か上位8bitがXBeeの固有アドレスである13A200に上書きされる

(APIコマンドを使えば一時的に0xFFFFにできるがUSBを抜くと?元に戻る) - 付属のターミナルで16進数が直接打ち込めない

- ブロードキャストしようとDestination Addressを0xFFFFにしようとすると、何故か上位8bitがXBeeの固有アドレスである13A200に上書きされる

これらの現象はWindows版では見られなかった。

XCTUがOSXに対応したのは最近らしいので、しばらくはWindows用を使うのが無難か?

EAGLEなんかもWindows版が使いやすいように感じた。

Windowsのほうがネットに情報が沢山転がっているので、無理してMACを使わないほうがいいかも?

- その他

I2Cは結構不安定?らしく、プログラムに問題が無くてもうまく通信できない場合がある(LCDを使っているときに原因不明の表示バグがでた)

ハンダ付けは部品を付ける場所と順番をよく考えないと、後で取り返しのつかないことになるかも(作品のユニバーサル基板の裏側はすごく残念なことになった)

6/24(火) 回路を基板実装する際の注意†

- まず電源回路を実装し、正しい電源電圧が得られるようになってから、その他のマイコン等部品をのせていく。(すべて実装すると、電源回路が正しくなかったときに部品が全滅する)

- 回路の動作確認やデバッグの際は、USB等から直接給電せず、必ず電流リミッタの掛けられる電源装置を使うこと。(回路に異常電流が流れ、部品の故障、最悪の場合事故や火災につながる)

- 電源装置からUSB等に給電できるように変換コネクタなどを各自用意しておくとよい。

マイクロUSBのコネクタについて

- マイクロUSBコネクタには向きが通常のものと逆のリバースがある。

- リバースが用いられることが多く、秋田先生のEAGLEライブラリもリバースである。

- 実装する際は必ずどちらを使うか確認すること。

- 他の部品についても、実際に使う部品の配線と回路図を必ずチェックしよう。思い込みは危険

6/26(木) 基板設計について書き忘れてたこと†

PCBを描くときに、ヘッダピンを回路に追加して、マイコンの書き込みに必要なピンとヘッダピンをつないでおくと、マイコンをハンダ付けした後でもヘッダピン用のホールを使って書き込みができるのでデバッグやチューニングに便利。

7/15(火) メールについて†

常識だが、メールを送るときは必ず自分の名前を忘れずに書く。

普段LINE等を使っているとついつい忘れてしまうが、読む人のことを考えてタイトルと名前くらいは必ず書こう。

名前、所属、連絡先などをまとめたテンプレートを作っておくと便利だが、iphoneのデフォルトメーラアプリにはテンプレ機能がないのが残念。

→設定→メール/連絡先/カレンダー→署名 から設定できる。

タイトルは簡潔に、返信の場合は勝手にタイトルを変えない等々も常識として押さえておく。

句読点の省略なんかも友達同士のメール以外では当然NG。

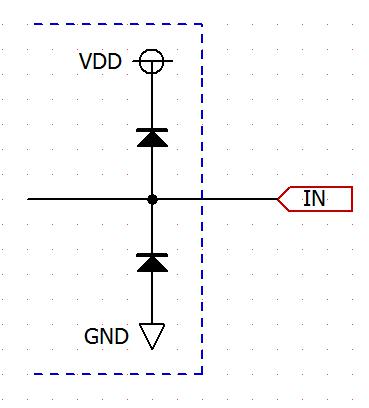

10/24(金) 入力ピンの保護回路†

マイコン等のICの入力ピンには、こんな感じの保護回路が入っている。

入力ピンに"1"を与えたままマイコン等のVDDを切っても、入力ピンから保護回路を通して、

(入力ピン電圧)-(ダイオードの電圧降下)

分の電圧が電源ラインに供給されてしまうため、ICの電源が落ちないことがある。

マイコンにリセットをかける時など、電源を一旦切りたい場合は、入力ピンに電圧が掛かっていないかを確認しよう。