- 履歴一覧

- 差分 を表示

- 現在との差分 を表示

- ソース を表示

- kawakami へ行く。

- 1 (2012-04-10 (火) 08:42:19)

- 2 (2012-04-10 (火) 08:42:41)

- 3 (2012-04-10 (火) 17:26:44)

- 4 (2012-04-13 (金) 18:20:07)

- 5 (2012-04-16 (月) 18:53:16)

- 6 (2012-04-18 (水) 00:31:13)

- 7 (2012-04-19 (木) 16:35:31)

- 8 (2012-04-19 (木) 23:18:28)

- 9 (2012-05-01 (火) 15:47:45)

- 10 (2012-05-01 (火) 15:47:45)

- 11 (2012-05-02 (水) 13:36:04)

- 12 (2012-05-31 (木) 16:21:36)

- 13 (2012-06-01 (金) 14:40:20)

- 14 (2012-06-01 (金) 14:51:31)

- 15 (2012-06-01 (金) 14:51:31)

- 16 (2012-06-02 (土) 22:47:14)

- 17 (2012-06-05 (火) 16:26:16)

- 18 (2012-06-05 (火) 16:26:16)

- 19 (2012-06-22 (金) 18:17:15)

- 20 (2012-06-25 (月) 23:14:54)

- 21 (2012-06-25 (月) 23:14:54)

- 22 (2012-07-25 (水) 19:41:48)

- 23 (2012-07-31 (火) 16:44:20)

- 24 (2012-08-02 (木) 19:03:34)

- 25 (2012-08-07 (火) 19:16:29)

- 26 (2012-08-08 (水) 18:34:42)

- 27 (2012-08-09 (木) 18:22:33)

- 28 (2012-08-10 (金) 12:45:35)

- 29 (2012-08-23 (木) 18:48:14)

- 30 (2012-08-28 (火) 17:14:11)

- 31 (2012-09-01 (土) 02:18:18)

- 32 (2012-09-03 (月) 02:55:13)

- 33 (2012-09-03 (月) 18:06:08)

- 34 (2012-12-04 (火) 18:32:46)

- 35 (2012-12-05 (水) 16:44:22)

- 36 (2013-02-08 (金) 14:22:24)

- 37 (2013-05-22 (水) 18:16:44)

- 38 (2013-05-29 (水) 10:59:41)

- 39 (2013-05-30 (木) 21:51:50)

- 40 (2013-06-01 (土) 00:00:22)

- 41 (2013-06-05 (水) 16:52:26)

- 42 (2013-06-06 (木) 15:17:47)

作業日誌†

目次

- 作業日誌

- 2012/12/04(Tue)

- 2012/09/03(Mon)

- 2012/09/02(Sun)

- 2012/08/31(Fri)

- 2012/08/28(Tue)

- 2012/08/23(Thu)

- 2012/08/09(Thu)

- 2012/08/08(Wed)

- 2012/08/07(Tue)

- 2012/08/02(Thu)

- 2012/07/31(Tue)

- 2012/07/25(Wed)

- 2012/06/25(Mon)

- 2012/06/22(Fri)

- 2012/06/05(Tue)

- 2012/06/01(Fri)

- 2012/05/31(Thu)

- 2012/05.02(Wed)

- 2012/05/01(Tue)

- 20120416(Mon)

- 20120413(Fri)

- 20120410(Tue)

2011年度分はMeRLサーバのほうにあります。

http://merl.ec.t.kanazawa-u.ac.jp/diary_private/index.php?kawakami

コメント†

最新の3件を表示しています。 コメントページを参照

2012/12/04(Tue)†

ISimのエラー(解決済み)†

ずいぶん久しぶりの作業日誌となってしまった。反省。

数日前からISimがエラーで落ちるようになってしまった。

エラー文面は以下の通り。

FATAL_ERROR:Simulator:Fuse.cpp:209:1.130.48.1 - Failed to compile one of the generated C files. Please recompile with -mt off -v 1 switch to identify which design unit failed. Process will terminate. For technical support on this issue, please open a WebCase with this project attached at http://www.xilinx.com/support.

FATAL_ERROR:Simulator:Fuse.cpp:209:1.130.48.1 - Failed to compile one of the generated C files. Please recompile with -mt off -v 1 switch to identify which design unit failed. Process will terminate. For technical support on this issue, please open a WebCase with this project attached at http://www.xilinx.com/support.

サポートに問い合わせて、とのことだったので秋田先生にXilinxサポートに投げていただいた。

その回答としては、メモリを10GB使っている。ModelSimを使うか、Linux版のISimを使って欲しいとのこと。

仕方なくModelSimについて調べていたところ以下のブログを発見。

http://marsee101.blog19.fc2.com/blog-category-66.html

少しエラーは違うが、Windows7 64bit版ではシミュレーションがうまくできないという内容だった。解決法として、Windows7 32bit版かWindows XP/Vistaの32/64bit版を使ってくれとのこと。

ダメ元でISEを32bit版で起動してシミュレーションを実行したところ正常にシミュレーションできた。32bitでの起動は以下をたどる。

Start -> すべてのプログラム -> Xilinx Design Tools -> ISE Design Suite 14.1 -> 32-bit Project Navigator

ここで起動したISEからプロジェクトを開く。

ちなみに自分のPCはWindows7 32bit メモリ4GBで、動いているISEはもちろん32bitだが恐らくメモリ不足で動かなかったのではないか。

ifdlkpはメモリを32GB搭載しているWIndows7 64bitで、64bitのためエラーが出たと思われる。32bitモードで起動すると正常動作する。

2012/09/03(Mon)†

System GeneratorとSimulinkを使ってみて(3)†

できないこともないが、やはり画像処理にはあまり向かないと思った。

重心を求める処理自体はそこまで難しくないからHDL書いて手動でインプリするのでもいいと思う。

メモ : 今後の方針†

重心を求める処理だけで視対象と眼球で1:1の対応が取れる座標が得られるのか実験してみる。さらにどれくらいばらつくのか(再現性はどの程度か)も調査。

影を含んだ状態でキャリブレーションでなんとかなるなら重心だけでいきたい。

2012/09/02(Sun)†

System GeneratorとSimulinkを使ってみて(2)†

引き続きSystem Generatorによる実装について試しているが、うまく進んでいない。

入出力+インバータだけのモデルでSimulink上でのシミュレーションもうまくいってるが、ucfファイルにてトップモジュールの入出力ピンの設定を行なっているがピン指定のところで存在しないなどのwarningが出ている。なんでだろう。

Simulinkモデル上ではモデルで表現されシンプルだが、生成されたHDLは分かりづらいかもしれない。

そうこうしているうちにMATLAB/Simulinkの試用期間が迫ってしまった...

2012/08/31(Fri)†

System GeneratorとSimulinkを使ってみて(1)†

インバータだけの簡単なモデルを作成してビットストリーム作成まで行った。しかしまだFPGA上で動作させることができていない。

ざっと見てみると、予めXilinxで用意してあるブロックしか使えないため、視線検出に使えそうな重心を求めるなどの処理は実装が難しい? 手動でインプリメントしたほうが無難かもしれない。

2012/08/28(Tue)†

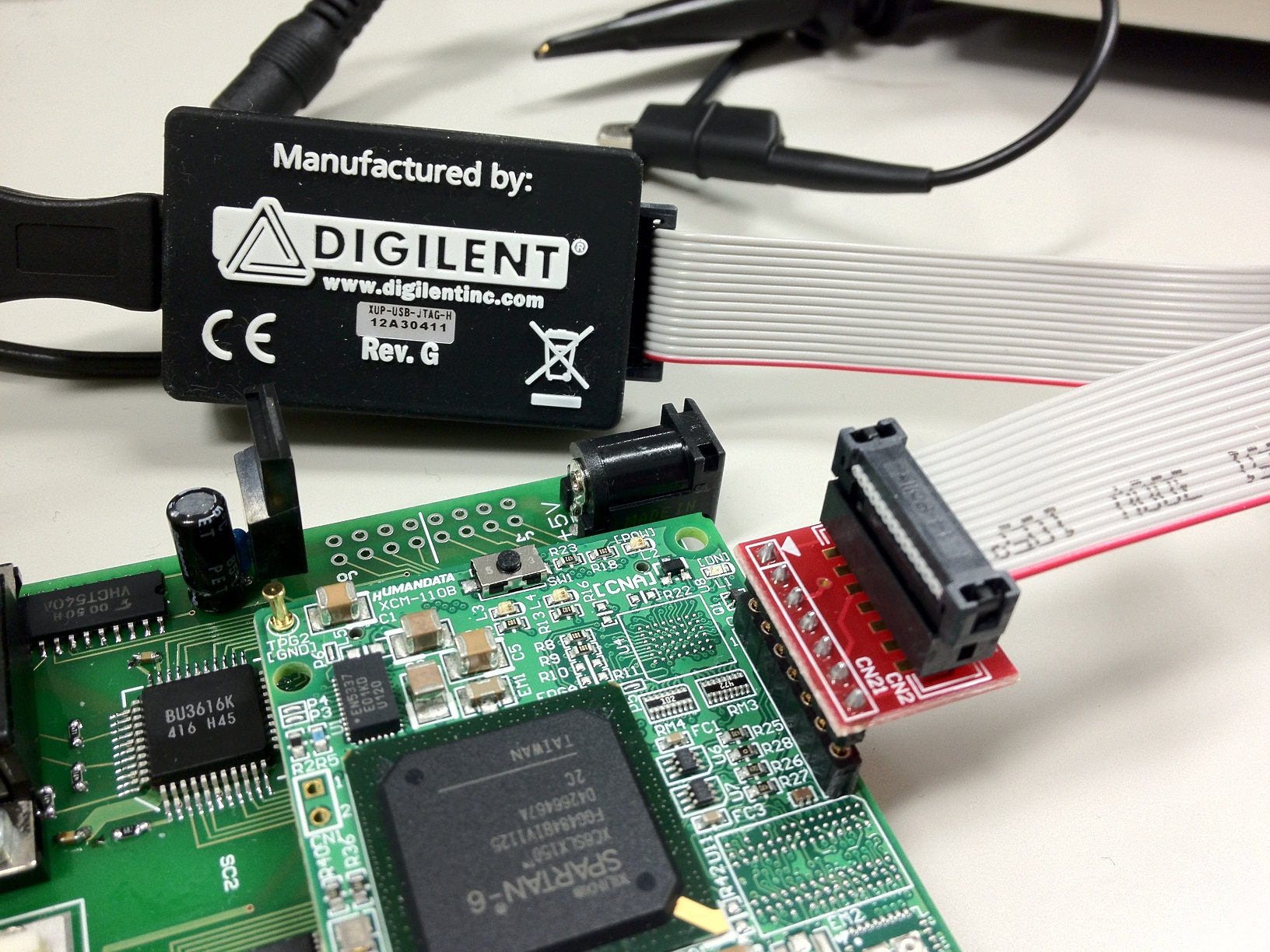

Digilent社製USB-JTAGケーブル†

ヒューマンデータで販売されているDigilent社製USB-JTAGケーブルを用意してもらったので、今後はこっちを使うことにする。ついでに付属していた2.0mm-2.54mmピッチ変換基板も組み立ててみた。

- 本体(XUP-USB-JTAG-H) : http://www.hdl.co.jp/ACC/XUPUSBJTAG/index.html

- 変換基板(ZKB-031) : http://www.hdl.co.jp/ZKB/ZKB-031/

Digilent社のXUP USB-JTAGケーブルは、Xilinx社のUSBダウンロードケーブルHW-USB(Platform Cable USB)の互換品で、Xilinx社のiMPACTから純正品と同じように使うことができます。 Digilent社はXilinx社のアライアンスパートナー企業です。

使い方はXILINXのPlatform Cable USBⅡと変わらない。コンピュータからもProgramming cables -> Xilinx USB Cableとして認識される。

小型になって便利。

2012/08/23(Thu)†

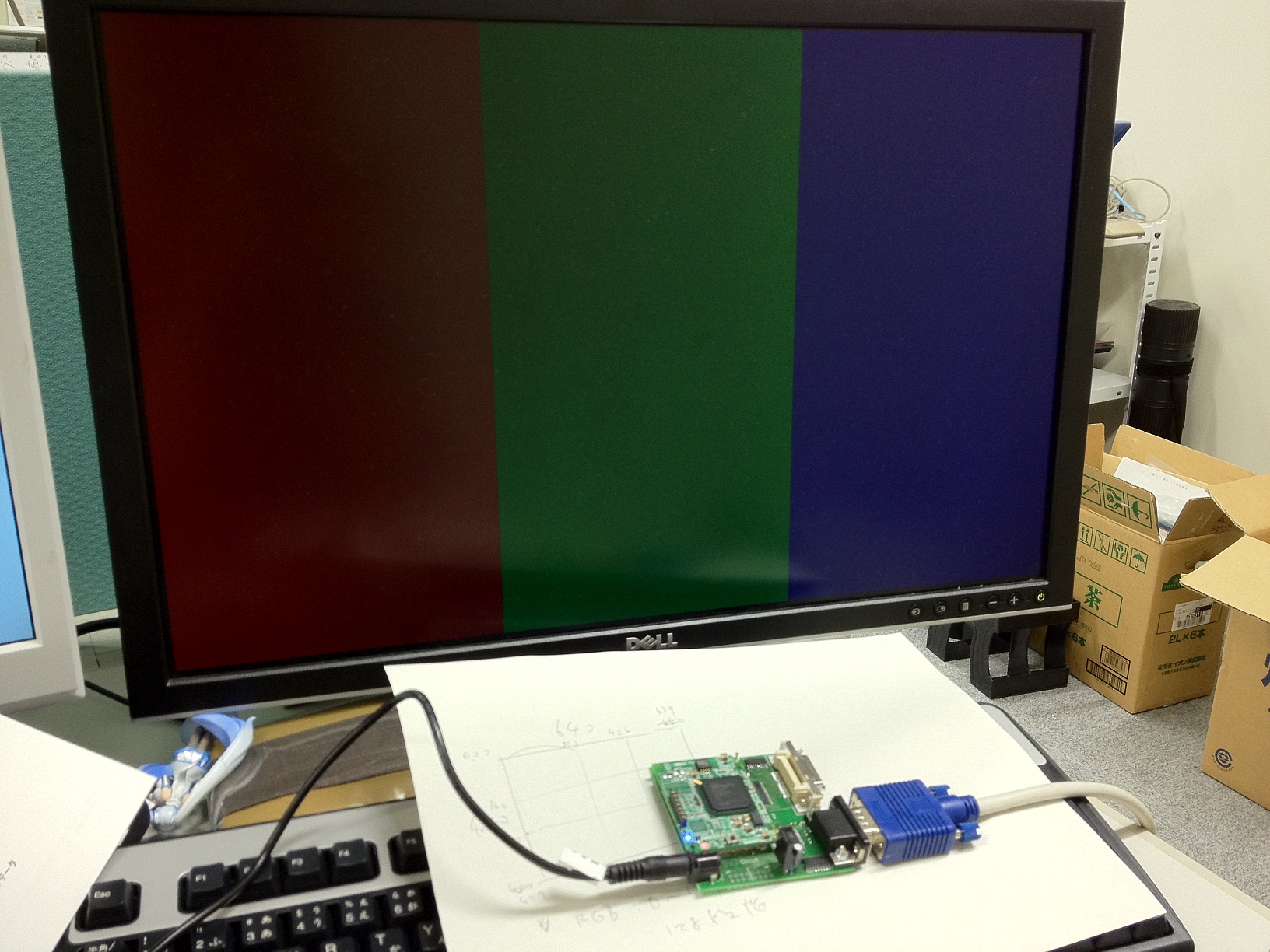

VGA出力成功†

うまくいってなかったVGA出力だが、クロック周りを見直したらあっけなく表示された。

(メモ : プロジェクト名gaTesSp6_120823)

2012/08/09(Thu)†

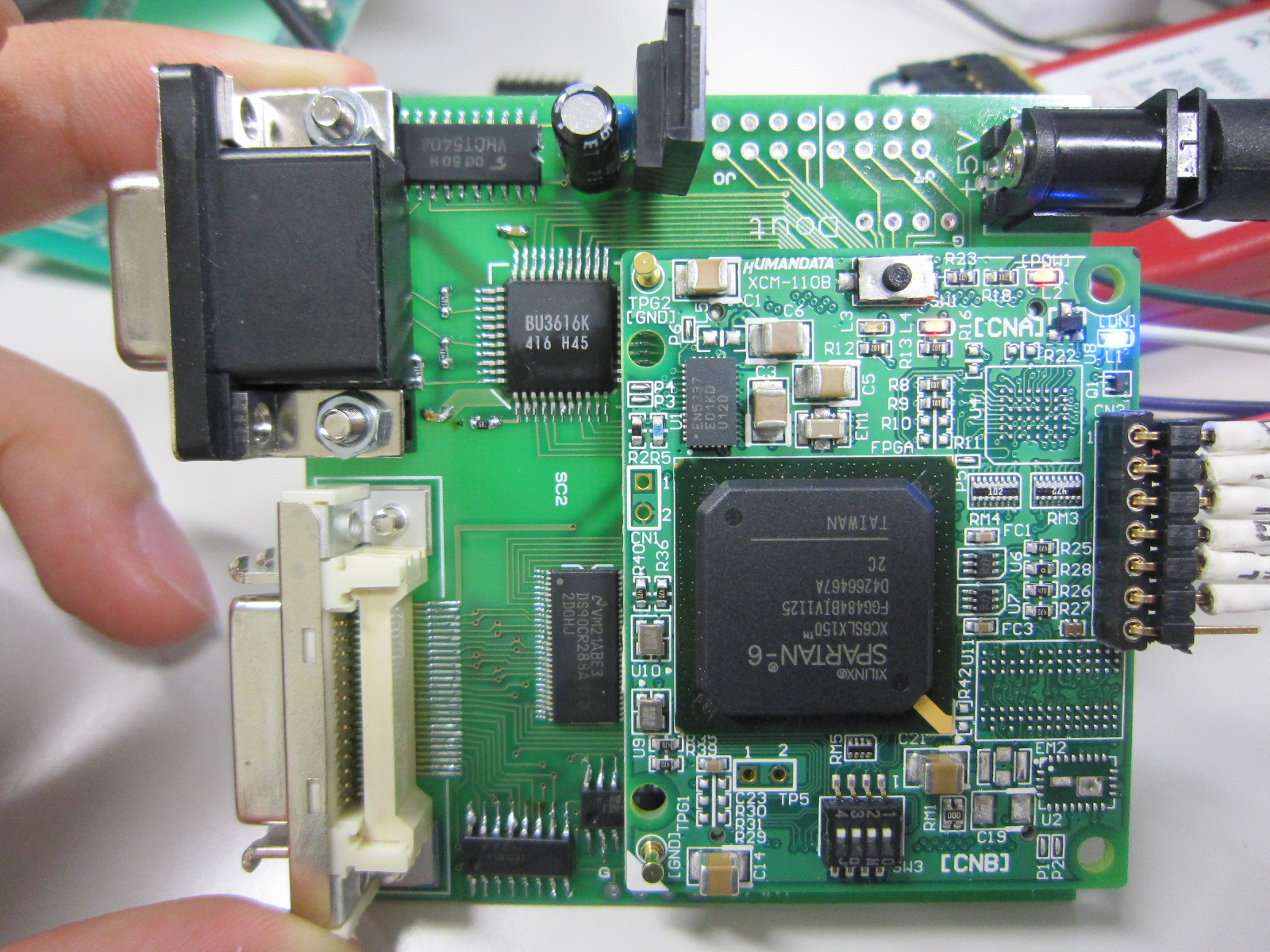

新しいSpartan-6ボード†

秋田先生に設計していただいた新しいSpartan-6用の基板とヒューマンデータのSpartan-6ボードを軽く触ってみた。

- 搭載FPGA : Spartan-6 XC6SLX150

- ボード : ヒューマンデータ製XCM-110B

- ベース基板 : 以下が1枚の基板に搭載されている

- CameraLinkコネクタ

- VGAコネクタ

- カメラ直結UART端子

- FPGAに繋がるUART端子

- 汎用ジャンパピン(8pin,

ショートさせると5VのHighに←3.3V動作のFPGAに5V入力?やはり誤りとのこと。パターンカットして3.3Vラインに接続予定(8/10))

とりあえずSpartan-6ボード上のLEDとスイッチを使って簡単な入出力のHDLとクロック分周+LED出力のHDLを書いたところ正常に動作させることができた。

ユーザーズマニュアルの最初のページに未使用ピンをFloatにする旨の注意があったためそれに従ってはじめに設定を行った。

JTAGピンの配置はVirtex-4と同様、コンフィグレーション手順も同じ。(Virtex-4のマニュアルに詳細手順有り)

ビットストリームファイルの割り当ての時に以下のような確認ダイアログが出たがNoを選択。

This device supports attached Flash PROMs. Do you want to attach an SPI or BPI PROM to this device?

WARNING:Xst:1710と1895†

論理合成段階で以下のwarningが出て何かと思ったら、26bit幅で宣言しているそのカウンタ内で常に24bit分しか使っていないという警告だった。

WARNING:Xst:1710 - FF/Latch <cnt_24> (without init value) has a constant value of 0 in block <spartan6tes120809>. This FF/Latch will be trimmed during the optimization process. WARNING:Xst:1895 - Due to other FF/Latch trimming, FF/Latch <cnt_25> (without init value) has a constant value of 0 in block <spartan6tes120809>. This FF/Latch will be trimmed during the optimization process.

これをカウンタの上限値いっぱいの24bit幅で宣言し直したら上記の警告は消えた。しかし一方でこんな警告が。

WARNING:HDLCompiler:413 - "C:\programming\xilinx\spartan6tes120809\spartan6tes120809.v" Line 42: Result of 25-bit expression is truncated to fit in 24-bit target.

途中で25bit幅の計算するけど、上位1bitは無視しちゃうよというwarningらしい。今回は無視しても問題なさそうなのでこのままにしておく。

2012/08/08(Wed)†

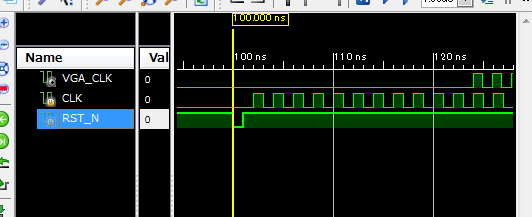

DCMによるクロック生成がうまくいかなかった原因†

昨日うまくいかなかったDCMによるクロックの生成だが、リセット入力であっさり解決した。

リセット入力は単純にRST_Nの信号にLowを与えればリセットがかかると思っていたが、重要なのは次にまたHighの状態に戻すことだった。前回はRST_NをLowにしたままクロックを与え続けて、DCMから出ない出ないという状態になっていた。実機でも動作確認。

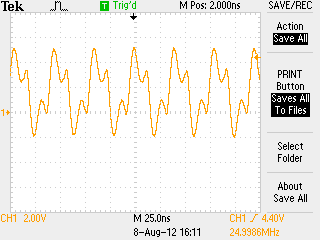

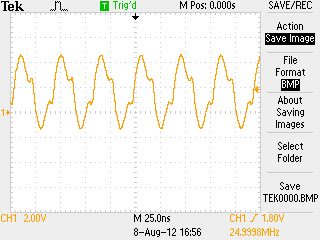

出力波形の歪み†

DCMで25MHzのクロックの生成はできたが、オシロで見ると波形がだいぶ歪んでいた。

秋田先生に見てもらったところ、信号端子とGNDとが離れすぎて電流ループができているのが原因とのこと。実際、より出力端子に近いところのGNDに繋いでみたところ歪みはかなり軽減された。

ucfファイルにおけるPERIOD制約†

先の波形歪みの原因が分かる前、ucfファイルでの設定に何か問題があるのかと思っていろいろ調べていたら、PERIOD制約なるものを見つけた。

25MHzで駆動する出力ピンに以下の記述を追加。

NET "VGA_CLK_25M" PERIOD = 40.0ns HIGH 50%;

しかしこれは入力ピンに対する制約だったはずとの指摘を受け、調べてみるとどうも確かに入力ピンに使う様子。

参考

タイミングについて

2012/08/07(Tue)†

DCMによるクロック生成がうまくいかない→解決†

前回設定したDCMを元に50MHzのクロックを出そうとしたが何も出てこない。明日もう一度見直してみる。

解決→2012/08/08(Wed)

2012/08/02(Thu)†

システム内のクロックの系統数†

同一システム内で複数のクロック源を使うのは良くない。基本的には1つ。

今回のVision Chipのシステムでは画像処理系はカメラからもらう40MHz、それ以外(VGA出力、UART、etc)はオンボードの48MHz辺りから取ると良い。

駒村さんのシステムではカメラの40MHz、オンボードの48MHz、18.432MHzの3系統を使用していた。

カメラの40MHzという数値はカメラの機種によって異なることがある点に注意。

18.432MHzというクロックの数値†

一見中途半端に見えるが、9,600bpsなどの数値を作りやすい。(整数で割り切れる)

ex) (18.432 * 10^6) / 9600 = 1920, 1920 / 96 = 20

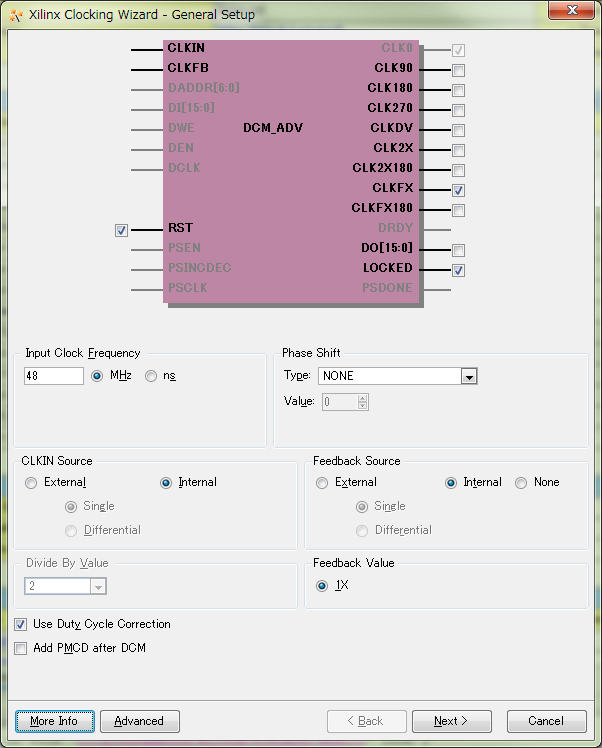

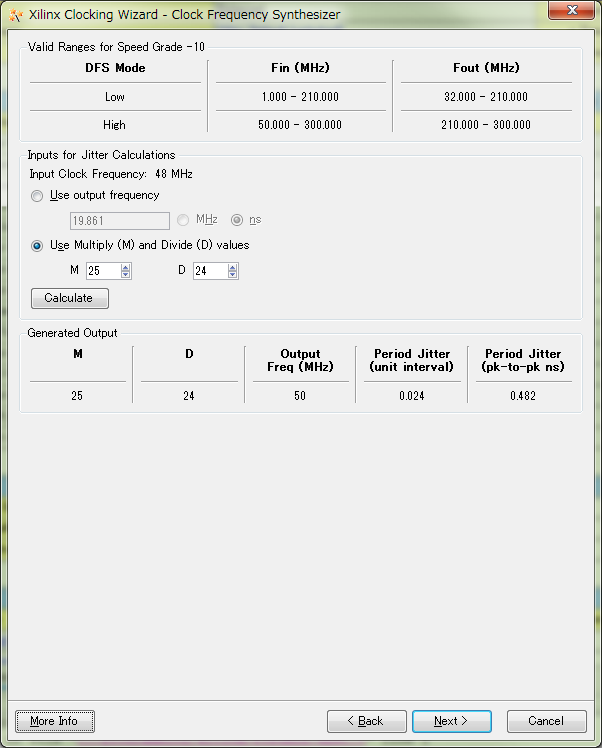

DCM(Digital Clock Manager)の設定†

XPGA上で様々なクロックを作れるDCMの設定。どうやって使うのか分からなくて先生にも聞いたりしたが駒村さんの日誌に普通にあった。ちゃんと調べる癖を付けよう...

- http://merl.ec.t.kanazawa-u.ac.jp/diary_private/index.php?komamura#kc8f40a7

- http://merl.ec.t.kanazawa-u.ac.jp/diary_private/index.php?komamura#z63041ce

- http://www.hdl.co.jp/xilinx/tpdcm/index.html

(参考)駒村さんの48MHzから50MHzクロックの生成パラメータ

CLKIN Sourceはボード上の48MHzだからExternalかと思ったが、駒村さんはInternalにしている。仕様書を見ると以下のようにある。

Spartan-3のDCM仕様書 : http://japan.xilinx.com/support/documentation/application_notes/j_xapp462.pdf CLKINをIBUFGグローバルバッファ入力プリミティブに接続する場合は[External]、その他のソースに接続する場合は[Internal]

2012/07/31(Tue)†

Evernoteが毎回同期に失敗する†

ここ1週間くらいMacBookAir上のEvernoteが同期に失敗する旨のメッセージを毎回出すようになって同期ができなくなってしまった。

ソフト再起動、Mac再起動、Evernote入れ直しをしても効果なし。

ヘルプ->アクティビティログのエラーメッセージ

2012-07-31 15:54:57 sync [ENSyncEngine] ERROR: exception adding note '情報通信と危機管理特論 2012年度前期' to server 2012-07-31 15:54:57 sync [ENSyncEngine] ERROR: Sync exception: EDAMUserException(errorCode:5,parameter:"Data.body")

これを見るととあるノートだけがエラーになっている様子。

そこでこのノートをコピーして、元のノートを削除したところ問題なく同期ができるようになった。

何が原因かは分からなかったが、1つ問題のあるノートがあると他のノートも全て同期できなくなる様子。ただしノートのダウンロードはできる。アップロードは無理。

2012/07/25(Wed)†

FPGA(VIRTEX4)を動かしたときのメモ†

FPGAでの簡単な動作確認に成功

ボード : XCM-202A

VIRTEX4 XC4VLX160

outTes120627で作業

メインのVerilog HDL

module outTes120627(IN_I, OUT_O);

input IN_I;

output OUT_O;

assign OUT_O = IN_I;

endmodule

制約ファイル

NET "IN_I" LOC = AK12; NET "OUT_O" LOC = AJ12; #NET "IN_I" IOSTANDARD = "LVCMOS"; #NET "OUT_O" IOSTANDARD = "LVCMOS";

LVCMOSのを有効にしたらエラー出てコメントアウトしたけど、ISEでまとめた後にピン割付のレポート見たらLVCMOSになってた。デフォルトだとこうなる?

参考 : http://www.kumikomi.net/archives/2009/05/ioledrs-232.php

.vファイルを書く→制約ファイル(.ucf)を書く

"FPGAボードで学ぶVerilog HDL"の手順に従った。

無事書き込みし、実行できた。

駒村さんのストレージかifDLのdropboxの"ifDL\Research\CameraLink"にある。

- XCM-202-main.pdf

コンフィグレーション方法、DIPスイッチの設定等が書いてある - ZKB041-sch.pdf

黒い基板とXCM-202Aとのピンアサインが書いてある - XCM-202A_pin2.xls

黒い基板とこっちで作った緑の基板のピンアサインが書いてある

詰まったところ

- Platform Cable USBⅡがiMPACT上で最初認識されなかった。

最初はOutput -> Cable setup...でパラレルポートを使う設定になっていたため検出されなかった。

それからVrefに関するエラーが出た。調べると正常なら本体のLEDの色が緑になるはずらしいが、現時点ではオレンジ。赤のVrefがVCCの供給ではなくてデバイスの電圧の検出用ではないかと思い、FPGAボードに3.3VをACアダプタから供給してみる。すると繋いだ瞬間に緑に変わった。

これでCable auto connectしてみると成功の表示。

XCM-202Aのドキュメントpdfの手順に従ってFile -> Initialize ChainしてみるとROMとFPGAが検出され、表示された。

2012/06/25(Mon)†

FPGAボード(XCM-202)JTAGコネクタ†

XILINX Platform Cable USBⅡから出てる"VREF/VREF"と書かれた赤い線と"---/INIT"と書かれた灰色の線がどう繋がるか分からなかったから駒村さんの作業日誌を見たら載っていた。

http://merl.ec.t.kanazawa-u.ac.jp/diary_private/index.php?komamura#mb76f860

赤はVCCとして見てよく、灰色はおそらく使わない。またFPGAボード側のGNDのうちの1つのピンは使わなくてよいらしい。

2012/06/22(Fri)†

Rohm180nの最新のテクノロジファイル†

北川先生作成の"MeRL設計導入教育コース(外部非公開)"にPDKインストールの方法から最新のテクノロジファイルの導入法まで記されている。

半田さんのインストーラでは古いテクノロジファイルが含まれているので注意

2012/06/05(Tue)†

FPGAについて†

使用するのはXILINXのFPGA。7, 8月くらいに笹田くん・自分用のボードが来そうなのでそれまで基礎の勉強。

- verilog-HDLの書き方

- ISEの使い方

- cameraLink規格の勉強

- カメラ信号の理解

まずはHDLの書き方の勉強を始めていきたい。

駒村さんの作業日誌等にいろいろなノウハウがあるのでそちらも探して読む。

2012/06/01(Fri)†

OpenCVを使った瞳孔中心推定ソフトウェアの続き†

昨日の続き

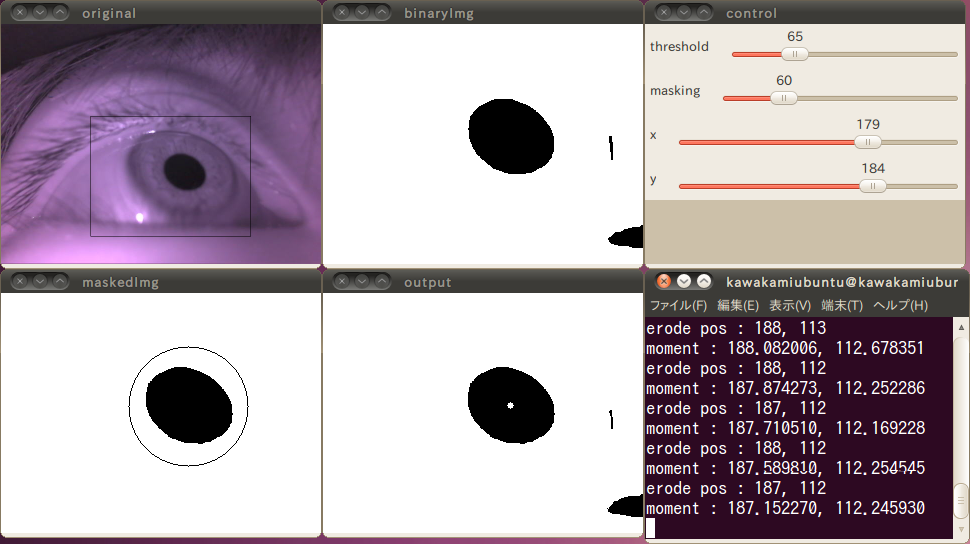

こんな感じ。撮影画像640x480のうち320x240を切り抜いて処理対象に。

撮影画像 二値化画像 コントロール

マスキング範囲 算出瞳孔中心(白い点) 座標出力

二値化画像で瞳孔以外の黒の領域があるが、マスキングで除去されて最終的な瞳孔領域の重心計算に影響していないことが分かる。

2012/05/31(Thu)†

眼球撮影用Webカメラの改良†

前回作製したカメラだと眼球を正面から撮影していたが、やはり下から見上げるような形で撮影したほうが瞳孔の欠けの影響を少なくできることが分かったのでカメラを下に設置し直した。

また、照射する赤外線も下から当てればプルキニエ像の映り込みを減らせるため位置を移動。

OpenCVを使った瞳孔中心推定ソフトウェア†

FPGAでの実装に先立って、OpenCVを使ってPC上で実際にWebカメラから取得した眼球画像から瞳孔の中心座標を求めるソフトウェアを作っている。

処理の流れは、

撮影

↓

収縮(0次モーメント=0になる直前まで繰り返し)

↓

1次モーメント算出(収縮できれいに1点に収まらないため1次モーメントで消失点座標を算出→整数化)

↓

マスク円作成

↓

マスキング

↓

1次モーメント算出

以上の処理で瞳孔の中心の算出ができた。

Webカメラは640x480で撮影しているが任意の区間を切り取って320x240にしている。

2012/05.02(Wed)†

sftpコマンド†

手元のMBAからVDECの20番サーバへファイルを置いた時のメモ

sftp (ユーザ名)@(20番サーバ)

put (ローカルのファイル名。TAB補完は効かなかった)

これでOK

2012/05/01(Tue)†

Phenitec INV設計と今後のメモ†

DRCはDivaを使う

撮像素子はダイオードのシミュレーションができないからpDは描かずにLVS

画素間を突っ切るような配線にはM1, 2で遮光も兼ねる。遮光のメインはM2

隙間の下にトランジスタが無ければ問題ない

素子内の配線にはゲートを使ってもいい

前田さんの不規則の素子のレイアウトを参考にするといいかも

20120416(Mon)†

ITU Gaze Tracker†

以前輪講で読んだ論文"An open-source low-cost eye-tracking system for portable

real-time and offline tracking"で使用されていたオープンソースのITU Gaze Trackerを使ってみた。

32bit Windows用のバイナリが入っていたのですぐに起動して試せる。

今の時点のバージョンは2.0ベータ。

100均でサングラスを買ってきてカメラと赤外線LEDを固定。

はじめにキャリブレーションがあり、9点、12点、16点が選べる。16点キャリブレーションをすると小さいボタンにもほぼ正確にポインタを視線により誘導できた。

精度は期待できそう。

今は眼球の正面にカメラが来ているが、斜め方向でも微妙な角度などによって上手くいったりそうでなかったり。正面からでもやはり影の影響などは大きい様子。

20120413(Fri)†

Arduino関連メモ†

- PC-Arduino間のシリアル通信の信号がTX/RXピンに出てくる

Arduino Uno R3で確認。

TX/RXピンにXBeeを繋いでいると書き込みに失敗するのでもしかしたらと思ってピンを見てみたら予想通り書き込みの信号がTX/RXピンに出てきていた。

書き込み時はここに繋がっているものがあればいちいち外す必要あり。それとPC向けとTX/RXピン向けで通信を分けることができないのはちょっと難点かも。 - IDEの書き込みポートの設定

なぜか忘れて書き込み失敗する。ちゃんと確認するようにしたい。

20120410(Tue)†

第2回Pheniecイメージセンサ試作MTG†

イメージセンサ試作では川粼、中村と共に画素を担当。

計画としては18日くらいまででインバータの設計練習終了後、25日くらいまでに画素回路設計完了。

INV設計練習メモ(1)†

画素は10ミクロン四方

W/Lは最小でおk

画素の注意。内部素子の位置は異なるけど、線の位置は全画素で同じにしないといけない

電源線、GND、行選択線、列選択線、リセット線の5本ある

セレクタ

NANDしか作れないけらNOTをその後ろに付けないといけない

いきなりNANDに大きいNOTを付けると負荷容量が大きくなりすぎて動作速度が落ちる

3つとか5つに分割して、小さいのから段々大きくしてみるといい