偙傟偵傛偭偰丄LED偺堦斣壓埵偺寘(LSB)偼1/1000昩亊24=16[ms]偛偲 偵僇僂儞僩偑憹偊偰偄偒傑偡丅 偙傟偱傕傑偩懍偡偓偰傢偐傝傑偣傫偑丄 LED偺堦斣忋埵偺寘(MSB)偱偼1/1000昩亊211=2048[ms]=栺2昩 偛偲偵僇僂儞僩偑憹偊傞偙偲偵側傝丄偙傟偱偁傟偽栚偱尒偰傢偐傝偦偆偱偡丅

1kHz偺僋儘僢僋怣崋偱僇僂儞僞傪摦嶌偝偣傞偲丄1kHz偺廃婜丄

偮傑傝1/1000昩偛偲偵僇僂儞僞偺抣偑憹壛偟偰偄偔偙偲偵側傝傑偡丅

偙傟傪LED側偳偱昞帵偟偰傕丄懍偡偓偰傢偐傝傑偣傫丅

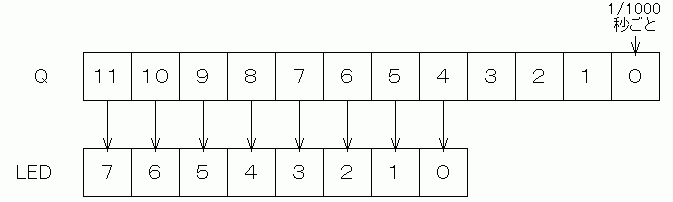

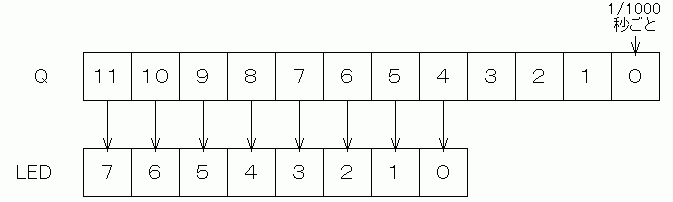

偦偙偱彮偟岺晇傪偟偰丄12價僢僩偺僇僂儞僞傪巊偄丄

偦偺忋埵偺8價僢僩暘偩偗傪丄LED偱昞帵偝偣偰傒傞偙偲偵偟傑偡丅

偙傟偵傛偭偰丄LED偺堦斣壓埵偺寘(LSB)偼1/1000昩亊24=16[ms]偛偲

偵僇僂儞僩偑憹偊偰偄偒傑偡丅

偙傟偱傕傑偩懍偡偓偰傢偐傝傑偣傫偑丄

LED偺堦斣忋埵偺寘(MSB)偱偼1/1000昩亊211=2048[ms]=栺2昩

偛偲偵僇僂儞僩偑憹偊傞偙偲偵側傝丄偙傟偱偁傟偽栚偱尒偰傢偐傝偦偆偱偡丅

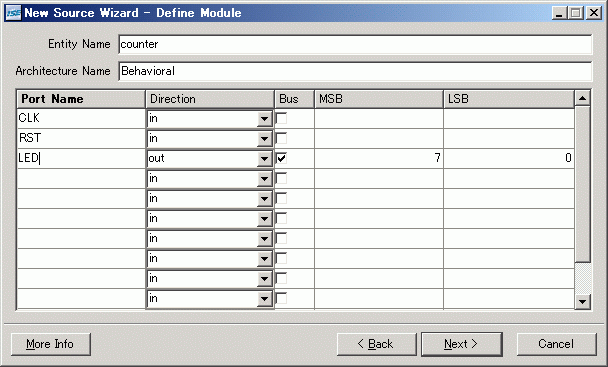

傑偢僾儘僕僃僋僩傪偮偔傝傑偡丅

柤慜偼counter偲偟偰偍偒傑偟傚偆丅

懕偄偰丄僇僂儞僞傪婰弎偡傞VHDL僼傽僀儖傪嶌傝傑偡丅

柤慜偼counter(counter.vhd)偲偟偰偍偒傑偟傚偆丅

懕偄偰擖弌椡傪掕媊偟傑偡丅

埲壓偺3偮偺怣崋傪掕媊偟偰偍偒傑偡丅

CLK偼僋儘僢僋丄RST偼儕僙僢僩丄LED(7)乣LED(0)偼丄

EDX-001忋偺8屄偺LED偵偮側偑傞弌椡偱偡丅

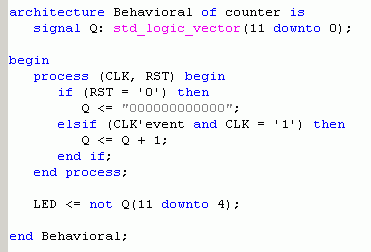

僇僂儞僞傪count.vhd偵VHDL偱婰弎偟偰偍偒傑偡丅

偙偺椺偱偼丄僇僂儞僞偺撪晹偵12價僢僩偺僇僂儞僩抣Q傪傕偪丄

偦偺忋埵8杮偩偗傪丄嵟屻偺曽偱弌椡LED偵愙懕偟偰偄傑偡丅

(EDX-001偺LED偑晧榑棟(0偱揰摂)側偺偱丄not傪偮偗偰愙懕偟偰偄傑偡)

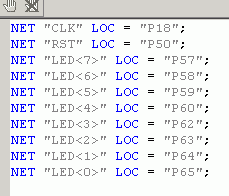

傑偨儕僙僢僩怣崋RST偼僋儘僢僋偲偼旕摨婜偵偟偰偁傝傑偡丅 偪側傒偵偙偺儕僙僢僩怣崋RST偼丄EDX-001偺僗僀僢僠A偵偮側偖傛偆偵 師偺僺儞掕媊僼傽僀儖偵婰弎偟傑偡丅 偮傑傝僗僀僢僠A傪墴偡偲儕僙僢僩偑偐偐傞傛偆偵偟傑偡丅

User Constrain撪偺Edit Constrains傪慖傫偱

僺儞掕媊僼傽僀儖傪嶌惉偟丄忋婰偺傛偆偵婰弎偟偰偍偒傑偡丅

偪側傒偵RST偼丄EDX-001忋偺僗僀僢僠A偑偮側偑偭偰偄傞P50(50斣僺儞)偵

偮側偘傞傛偆偵巜掕偟偰偄傑偡丅

(偙偺P50偼丄戞4夞偺墘廗偱偼PSW_A偲偄偆柤慜偵偟偰偄偨怣崋偱偡)

偁偲偼榑棟崌惉偐傜彂偒崬傒僼傽僀儖偺惗惉傊恑傒丄 counter.bit偑偱偒偨傜丄copy僐儅儞僪偱揮憲偟偰摦嶌偝偣偰傒傑偟傚偆丅

嵍忋偺夋柺偱Behavioal Simulation傪慖傃丄

僥僗僩儀儞僠偺僼傽僀儖(test_counter.vhd)傪怴婯偵捛壛偟丄

忋婰偺傛偆偵婰弎偟偰偍偒傑偡丅

嵟弶偺100ns娫偩偗RST=0偲偟偰儕僙僢僩傪偐偗偰偄傑偡丅

傑偨屻敿偺process暥偱偼丄RST怣崋傪曄壔偝偣偰偄傞偺偲偼

撈棫偵丄50ns偛偲偵CLK偺抣傪斀揮偟偰偄傑偡丅

偮傑傝CLK偼丄50ns偛偲偵0仺1仺0仺1仺丒丒丒偲側傝傑偡偺偱丄

曄壔偺廃婜偼100ns丄偮傑傝10MHz偺僋儘僢僋怣崋丄偲偄偆偙偲偵側傝傑偡丅

(偙傟偼幚嵺偵梌偊傞1kHz傛傝偼1000攞懍偄偱偡偑丄

崱夞偼婥偵偟側偄偙偲偵偟傑偡)

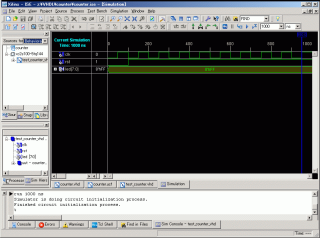

僔儈儏儗乕僔儑儞傪幚峴偡傞偲丄偙偺傛偆偵側傝傑偡丅

counter偺弌椡偱偁傞LED偺抣偺攇宍偑尰傟傑偡偑丄

FF偱曄壔偟偰偄傑偣傫丅

偙傟偼丄LED偼僇僂儞僞偺忋埵8價僢僩偩偗傪偮側偄偱偁偭偨偺偱丄

傑偩曄壔偑尰傟偰偄側偄偨傔丄偱偡丅

(CLK偺16敪栚偱偼偠傔偰LED偑曄壔偡傞偼偢)

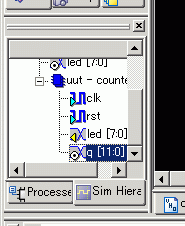

偦偙偱丄僇僂儞僞偺撪晹偵偁傞僇僂儞僩抣偱偁傞Q偺抣傕

僔儈儏儗乕僔儑儞偱妋擣偟偰傒傞偙偲偵偟傑偟傚偆丅

嵍懁偺Sim Hierarchy偺夋柺撪偱丄僔儈儏儗乕僔儑儞懳徾偺夞楬counter傪

奐偒丄偦偺拞偵偁傞q[11:0]傪攇宍偺夋柺傊僪儔僢僌偟偰偍偒傑偡丅

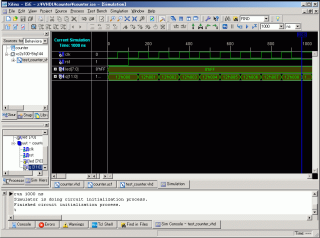

偦傟偐傜嵞搙僔儈儏儗乕僔儑儞傪峴偆偲丄q偺抣偑

CLK偺棫偪忋偑傝偛偲偵憹偊偰偄偭偰偄傞偺偑傢偐傝傑偡丅

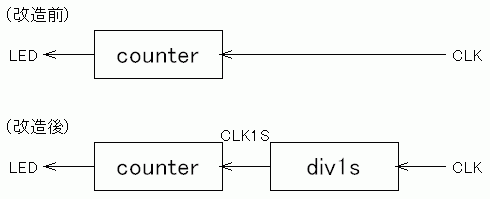

偙傟偵偼丄1kHz偺僋儘僢僋怣崋CLK傪捈愙僇僂儞僞偵梌偊傞偺偱偼側偔丄

偦傟偐傜1昩廃婜偺僋儘僢僋怣崋CLK1S傪嶌傝丄偦傟傪

僇僂儞僞偵梌偊傞傛偆偵偟偰傒傑偡丅

CLK偺傛偆偵懍偄僋儘僢僋偐傜CLK1S偺傛偆偵抶偄僋儘僢僋傪嶌傞夞楬傪

暘廃夞楬(divider)偲屇傃傑偡丅

崱夞巊偆暘廃夞楬偵偼div1s偲偄偆柤慜傪偮偗偰偍偔偙偲偵偟傑偡丅

傑偢div1s傪component偲偟偰巊偄丄偦傟偐傜弌椡偝傟偰偔傞

僋儘僢僋怣崋CLK1S傪巊偭偨僇僂儞僞夞楬傪偮偔偭偰偍偒傑偡丅

愭傎偳偮偔偭偨counter傪夵憿偡傟偽傛偄偱偟傚偆丅

偮偄偱偵丄偣偭偐偔側偺偱丄僇僂儞僩抣Q傪丄偦偺傑傑偡傋偰LED傊

偮側偄偱偍偒丄偦傟偵偁傢偣偰僇僂儞僩抣Q傕8價僢僩偵偟偰偍偒傑偡丅

傑偨CLK1S傪signal偲偟偰愰尵偟偰偍偒傑偡丅

摨條偵暘廃夞楬div1s傪丄怴偟偄VHDL僼傽僀儖偲偟偰丄

counter.vhd偵懳偟偰怴婯偵捛壛傪偟偰偍偒傑偡丅

柤慜偼div1s.v偲偟偰偍偗偽傛偄偱偟傚偆丅

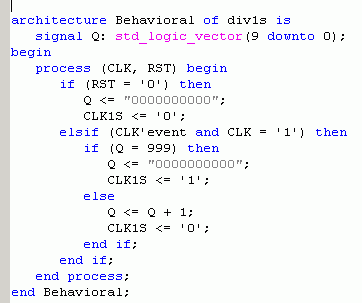

偦偺拞恎偺暘廃夞楬偼丄忋婰偺傛偆偵婰弎偟偰偍偒傑偡丅

暘廃夞楬傕丄幚偼僇僂儞僞偱偡丅 偨偩偟僇僂儞僩抣偵墳偠偰丄暘廃屻偺僋儘僢僋弌椡偱偁傞CLK1S傪 曄壔偝偣偰偄傑偡丅 偙偺椺偱偼丄CLK偺棫偪忋偑傝偛偲偵丄 Q=999側傜偽Q=0丄CLK1S=1偲偟丄 偦偆偱側偗傟偽Q偵1傪壛偊偰CLK1S=0偲偟偰偄傑偡丅

偙傟偵傛傝丄CLK偺棫偪忋偑傝偛偲偵Q偼0仺1仺丒丒丒仺999仺0仺1仺丒丒丒 偲曄壔偟偰堄婥丄999仺0偺偲偒偩偗CLK1S=1丄偦傟埲奜偱偼CLK1S=0偲 側傝傑偡丅 偟偨偑偭偰CLK1S偼丄CLK偺1000敪偛偲偵0仺1偲側傞偙偲偵側傝丄 CLK偺1/1000偺廃攇悢偲側傝傑偡丅 崱夞偼CLK偼1kHz偱偟偨偺偱丄CLK1S偼1Hz丄偮傑傝1昩廃婜偵側傝傑偡丅

偙偺挷巕偱峴偗偽丄偳偺傛偆側廃攇悢偺僋儘僢僋偱傕嶌傟偦偆偱偡偹丅

偪側傒偵div1s偺撪晹偺僇僂儞僩抣Q偑10價僢僩偲側偭偰偄傑偡偑丄 偦偺棟桼傪峫偊偰偍偒傑偟傚偆丅

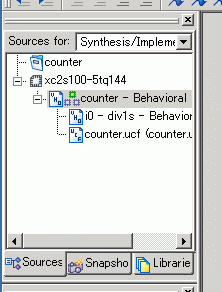

偪側傒偵div1s.vhd傪嶌惉偡傞偲丄counter偺拞偵

僀儞僗僞儞僗i0偲偟偰屇傃弌偝傟偰偄傞偙偲偑丄

Sources夋柺偱傕妋擣偱偒傑偡丅

奺夞楬偺梫揰傪傑傔偰偍偒傑偡丅 乮愝寁椺乮VHDL僼傽僀儖丒ucf僼傽僀儖堦幃乯乯

entity counter is

Port ( CLK : in STD_LOGIC;

RST : in STD_LOGIC;

LED : out STD_LOGIC_VECTOR (7 downto 0);

SG : out std_logic_vector(7 downto 0);

SA : out std_logic_vector(3 downto 0));

end counter;

architecture Behavioral of counter is

signal Q: std_logic_vector(3 downto 0);

signal CLK1S: std_logic;

signal SGb: std_logic_vector(7 downto 0);

component div1s

port (

CLK: in std_logic;

CLK1S: out std_logic;

RST: in std_logic

);

end component;

component dec7seg

port (

D: in std_logic_vector(3 downto 0);

SG: out std_logic_vector(7 downto 0);

SA: out std_logic_vector(3 downto 0)

);

end component;

begin

i0: div1s port map(CLK=>CLK, CLK1S=>CLK1S, RST=>RST);

i1: dec7seg port map(D=>Q, SG=>SGb, SA=>SA);

process (CLK1S, RST) begin

if (RST = '0') then

Q <= "0000";

elsif (CLK1S'event and CLK1S = '1') then

if (Q = 9) then

Q <= "0000";

else

Q <= Q + 1;

end if;

end if;

end process;

SG <= not SGb;

LED <= "1111" & not Q;

end Behavioral;

entity dec7seg is

Port ( D : in STD_LOGIC_VECTOR (3 downto 0);

SG : out STD_LOGIC_VECTOR (7 downto 0);

SA : out STD_LOGIC_VECTOR (3 downto 0));

end dec7seg;

architecture Behavioral of dec7seg is

begin

process (D) begin

case D is

when "0000" => SG <= "00111111";

when "0001" => SG <= "00000110";

when "0010" => SG <= "01011011";

when "0011" => SG <= "01001111";

when "0100" => SG <= "01100110";

when "0101" => SG <= "01101101";

when "0110" => SG <= "01111101";

when "0111" => SG <= "00100111";

when "1000" => SG <= "01111111";

when "1001" => SG <= "01101111";

when others => SG <= "00000000";

end case;

end process;

SA <= "1110";

end Behavioral;