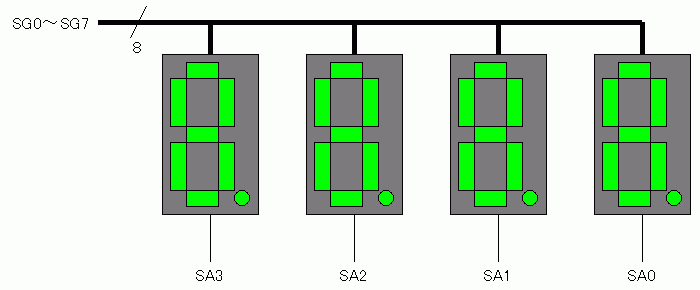

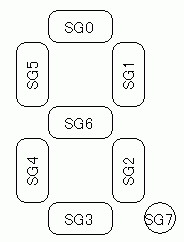

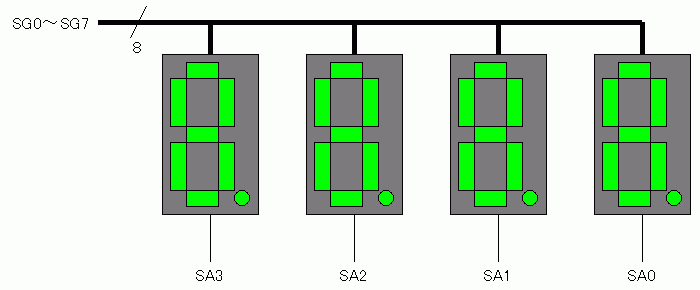

この調子で4桁もいけばよいように思えますが、残念ながら そう簡単にはいきません。 というのも、4個の7セグメントLEDは、SG0〜SG7が 共通につながっています。 つまりSG0='0'とすると、4桁のすべての7セグメントLEDの 上のLED(セグメント)が点灯してしまうことになります。

この調子で4桁もいけばよいように思えますが、残念ながら

そう簡単にはいきません。

というのも、4個の7セグメントLEDは、SG0〜SG7が

共通につながっています。

つまりSG0='0'とすると、4桁のすべての7セグメントLEDの

上のLED(セグメント)が点灯してしまうことになります。

これでは、好きな4桁の数値を表示できないわけですが、 その代わり、各桁を点灯させるか消灯させるかを決める SA0〜SA3という信号があり、これもFPGAにつながっています。 これは、(負論理なので)'0'になった桁の7セグメントLEDのみ、 SG0〜SG7に対応して各LED(セグメント)が点灯する、という 機能をもっています。

これをうまく使うと、次の4つの状態を順に変えていけば、 1桁ずつ数値を表示できることになります。

entity counter1 is

Port ( CLK : in STD_LOGIC;

RST : in STD_LOGIC;

Q : out STD_LOGIC_VECTOR (3 downto 0);

CO : out STD_LOGIC);

end counter1;

参考:設計例

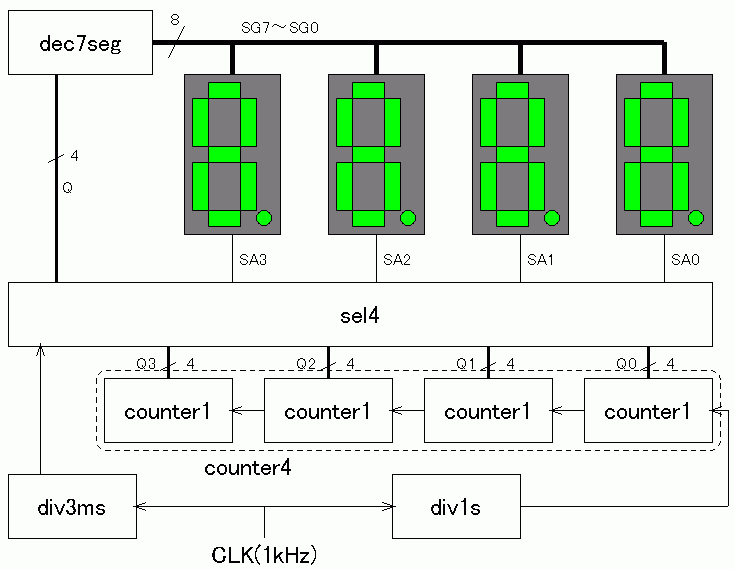

entity counter4 is

Port ( CLK : in STD_LOGIC;

RST : in STD_LOGIC;

Q0 : out STD_LOGIC_VECTOR (3 downto 0);

Q1 : out STD_LOGIC_VECTOR (3 downto 0);

Q2 : out STD_LOGIC_VECTOR (3 downto 0);

Q3 : out STD_LOGIC_VECTOR (3 downto 0);

CO : out STD_LOGIC);

end counter4;

参考:設計例

entity dec7seg is

Port ( D : in STD_LOGIC_VECTOR (3 downto 0);

SG : out STD_LOGIC_VECTOR (7 downto 0));

end dec7seg;

entity sel4 is

Port ( CLK : in STD_LOGIC;

RST : in STD_LOGIC;

Q0 : in STD_LOGIC_VECTOR (3 downto 0);

Q1 : in STD_LOGIC_VECTOR (3 downto 0);

Q2 : in STD_LOGIC_VECTOR (3 downto 0);

Q3 : in STD_LOGIC_VECTOR (3 downto 0);

Q : out STD_LOGIC_VECTOR (3 downto 0);

SA : out STD_LOGIC_VECTOR (3 downto 0));

end sel4;

※ヒント:これは、1の桁〜1000の桁を表示している状態4つの状態

SA0_ST〜SA3_STをもつステートマシンとして設計できそうです。

entity div1s is

Port ( CLK : in STD_LOGIC;

CLK1S : out STD_LOGIC;

RST : in STD_LOGIC);

end div1s;

entity div3ms is

Port ( CLK : in STD_LOGIC;

CLK3MS : out STD_LOGIC;

RST : in STD_LOGIC);

end div3ms;

※3msごとに桁が切り替わり、4桁でひとまわりですから、

表示の点滅の周期は3ms×4=12ms、つまり約80Hzということになります。

entity top_counter4 is

Port ( CLK : in STD_LOGIC;

RST : in STD_LOGIC;

SG : out STD_LOGIC_VECTOR (7 downto 0);

SA : out STD_LOGIC_VECTOR (3 downto 0);

LED0 : out STD_LOGIC);

end top_counter4;

NET "CLK" LOC = "P18"; NET "RST" LOC = "P50"; NET "LED0" LOC = "P65"; NET "SG<7>" LOC = "P29"; NET "SG<6>" LOC = "P30"; NET "SG<5>" LOC = "P31"; NET "SG<4>" LOC = "P40"; NET "SG<3>" LOC = "P41"; NET "SG<2>" LOC = "P42"; NET "SG<1>" LOC = "P43"; NET "SG<0>" LOC = "P44"; NET "SA<3>" LOC = "P46"; NET "SA<2>" LOC = "P47"; NET "SA<1>" LOC = "P48"; NET "SA<0>" LOC = "P49";

NET "LED0" LOC = "P65"; NET "LED1" LOC = "P64"; NET "LED2" LOC = "P63"; NET "LED3" LOC = "P62"; NET "LED4" LOC = "P60"; NET "LED5" LOC = "P59"; NET "LED6" LOC = "P58"; NET "LED7" LOC = "P57"; NET "SWA" LOC = "P50"; NET "SWB" LOC = "P51"; NET "SWC" LOC = "P54"; NET "SWD" LOC = "P56"; NET "BUZ" LOC = "P96"; NET "CLK0" LOC = "P88"; NET "CLK1" LOC = "P91";