第8・9回: 実習(4・5): FPGAへの論理回路の実装(ステートマシン)

前回構成をみてきたステートマシンの例であるタイマ(timer)を

実際にEDX-001に実装して動作させてみましょう。

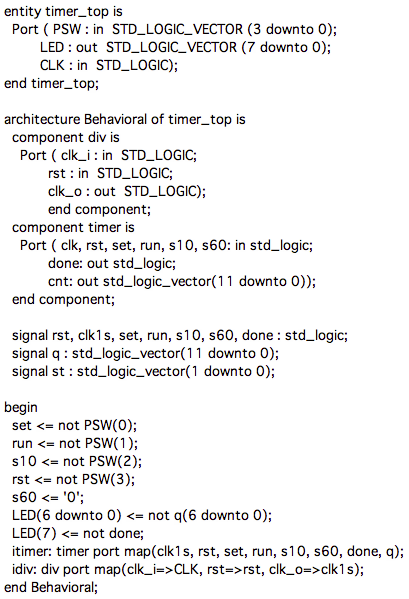

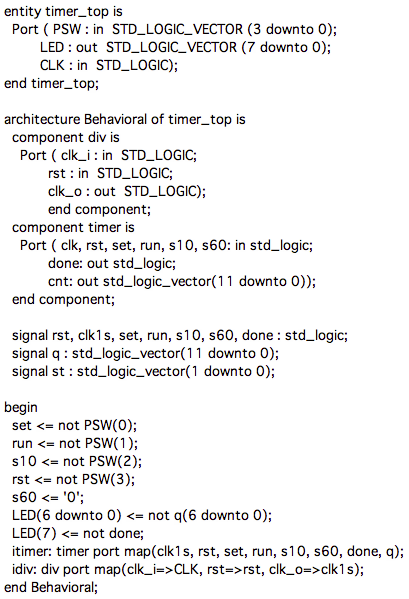

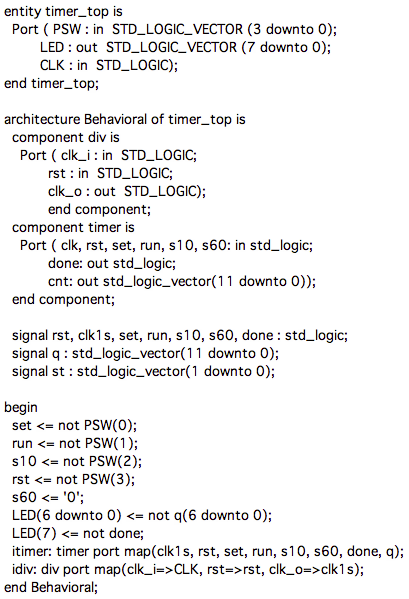

全体構成

全体構成は、以下の通りです、

- timer_top : トップ階層。スイッチ、LED、クロック信号(1kHz)を接続

- timer : 前回設計したタイマ

- div : 分周回路。実習(3)で作ったのと同じもの。

プロジェクトの作成・動作

実習(1)・実習(2)・

実習(3)と同様に、

Xilinx ISE Project Navigatorを使ってVHDL記述の論理回路の

設計と論理合成(コンパイル)を行います。

- File→New Projectで、新しいプロジェクトの作成を開始します。

プロジェクト名は"timer_top"としておきましょう。

- "Create a new source"(新規にファイルを作る)の画面で、

以下の4つのファイルを作成する。(いずれもVHDL module)

- timer_top (トップ階層)

- timer (タイマ全体)

- datapath (タイマのデータパス)

- control (タイマの制御部)

- div (分周回路:1/1000)

ちなみにtimer_topは、こちらを参考にするとよいでしょう。

※微妙にトラップが張ってあるので、内容をよく理解し、

間違いがあれば修正しながらながら入力すること。

その他のVHDLファイルも、新規作成で作られるひな形に、

第7回の資料を参考に、

内容をよく理解しながら記述を追記していくこと。

- "Add extisting sources"では、ピン配置指定ファイルedx001.ucfをダウンロードしておき、これを指定して追加する。

あとは論理合成をかけ、EDX-001に転送して動作させてみましょう。

※timer全体が、1Hzのクロックに同期して動作していることに注意。

つまり各ボタンは少し長めに押さないと反応しないように見える。

※動作が怪しいときは、例えばclk1s (1Hzのクロック)をどこかのLEDに接続して

点滅するかを確認するなどしてデバッグするとよいでしょう。

「構成を意識しない記述」によるtimer

別プロジェクトとして、「構成を意識しない記述」によってtimer.vhdを作成し、

動作させてみましょう。

余裕があれば、論理合成の結果(回路規模など)を比較してみましょう。

"Report Summary"から論理合成の結果(回路規模や動作速度など)を確認できます。

ただし今回のtimerぐらいの規模の回路では、Xilinx ISEの論理合成の最適化が

よく効くのか、両者の差はほとんど出ないようです。

戻る